IBM

Field Engineering Theory of Operation

Processing Unit System/360 Model 30 This manual contains information about the IBM 2030 Processing Unit. A companion manual, IBM 2030 I/O Control, Theory of Operation Manual, Form Y24-3362, should be obtained for information pertaining to the attachment of I/O devices to the IBM System/360 Model 30. For maintenance information on the IBM 2030, refer to the IBM 2030 Maintenance Manual, Form Y24-3390. The IBM 2030 Maintenance Diagram Manual, Form Y24-3466, contains flowcharts of specific op-code microprograms for the basic machine and the IBM 1400 Compatibility Feature. The IBM 1620 Compatibility Feature Diagram Manual, Form Y25-3478, contains flowcharts of 1620 emulation.

The following SRL publications contain much useful information about operation and application of the IBM System/360 Model 30:

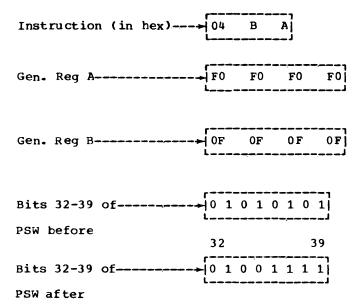

|     |            | Form   |                               |          |

|-----|------------|--------|-------------------------------|----------|

| IBM | System/360 | Model  | 30 Functional Characteristics | A24-3231 |

| IBM | System/360 | Model  | 30 Configurator               | A24-3232 |

| IBM | System/360 | Model  | 30 1401 Compatibility Feature | A24-3255 |

| IBM | System/360 | Model  | 30 1620 Compatibility Feature | A24-3365 |

| IBM | System/360 | Model  | 30 Operators Guide            | A24-3373 |

| IBM | System/360 | Model  | 30 Channel Characteristics    | A24-3411 |

| IBM | System/360 | Princi | ples of Operation             | A22-6821 |

#### Fifth Edition, June 1967

This edition, Y24-3360-1, is a minor revision of the previous edition, Y24-3360-0, but does not obsolete it. Minor changes, which are primarily in the IBM 1620 Compatibility Feature section, are marked by a vertical line to the left of the affected text, or by a dot ( $\bullet$ ) next to the title of an affected figure. In addition, other nontechnical, typographical corrections have been made throughout the manual.

Significant changes or additions to the specifications contained in this publication will be reported in subsequent revisions or in FE Supplements.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. 171, PO 6, Endicott, New York. Address comments concerning the manual to this address.

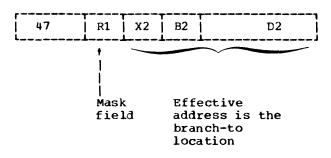

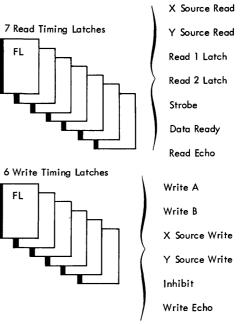

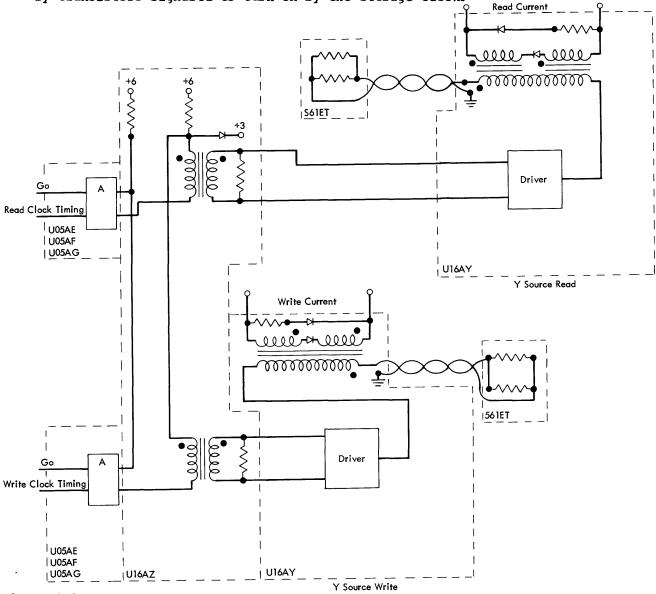

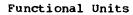

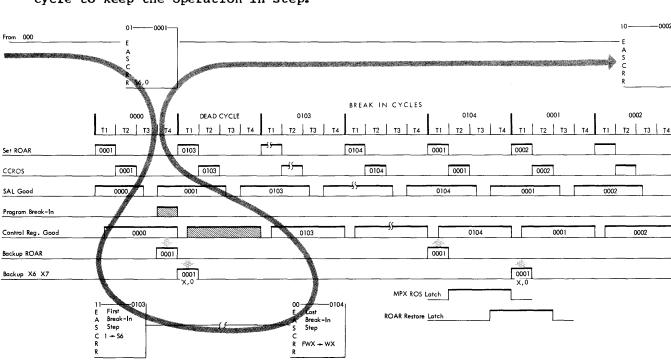

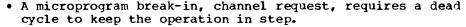

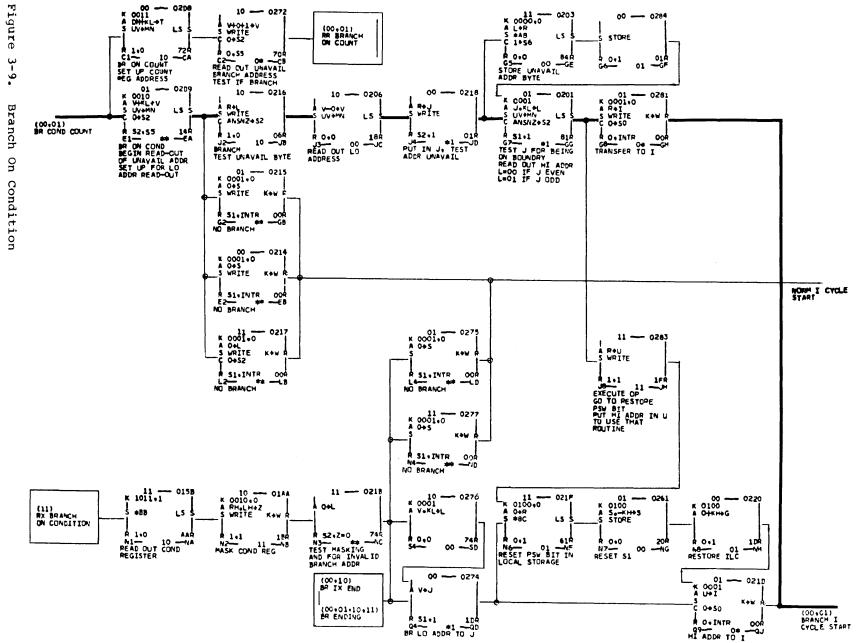

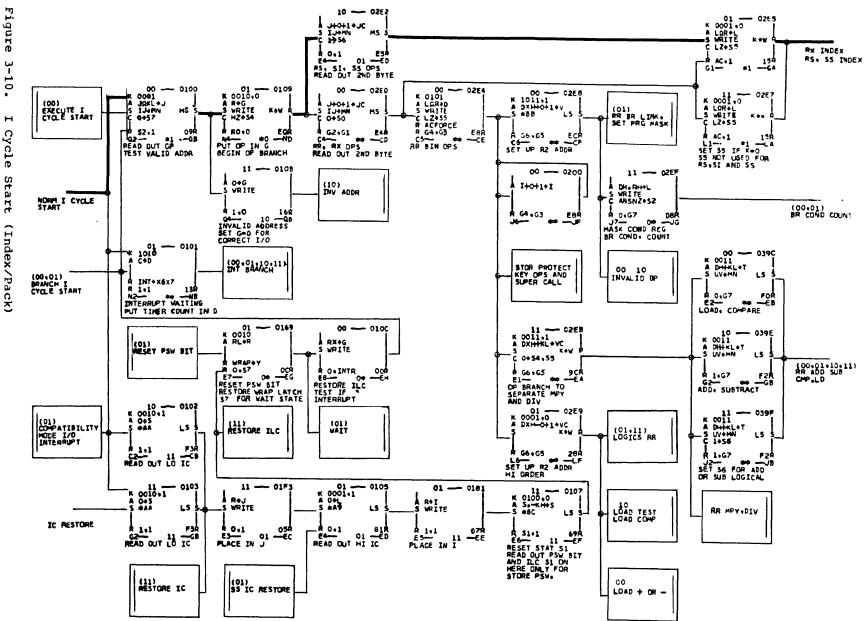

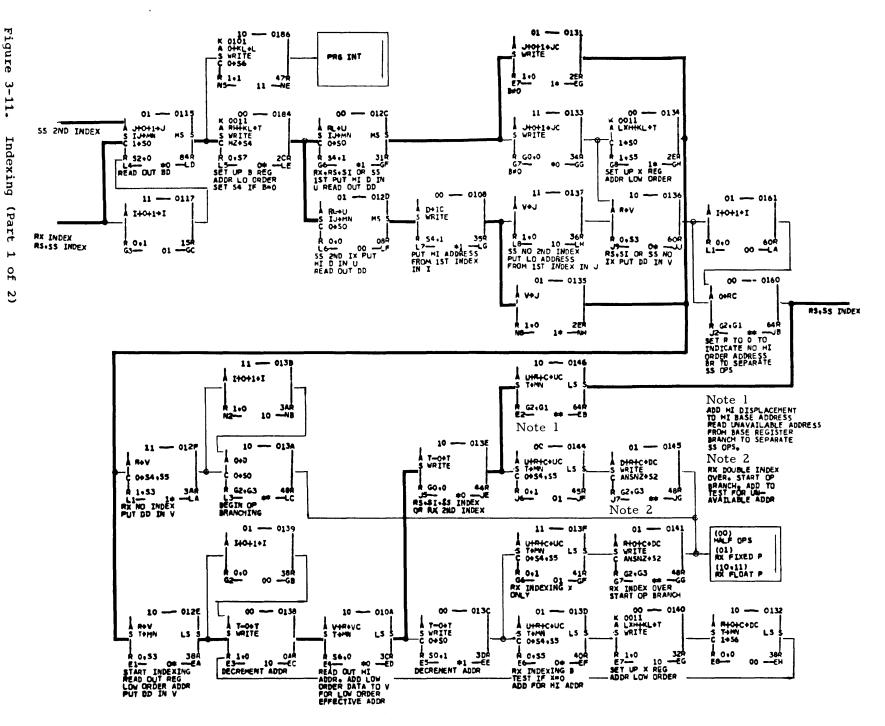

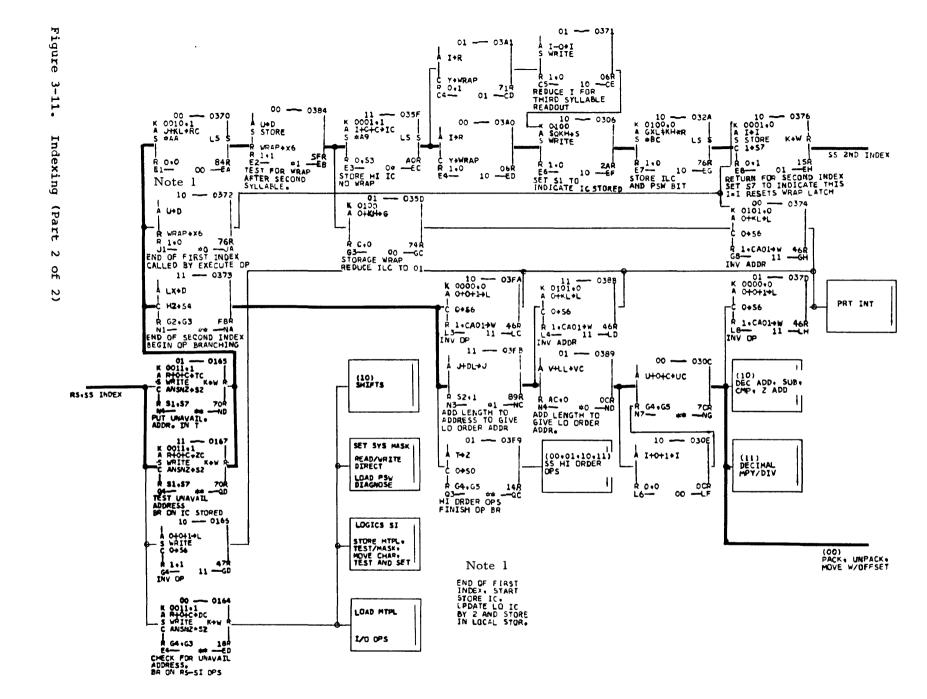

CHAPTER 1. INTRODUCTION. . . . . . 1-1 Overall Data Flow . . . . . . . . . . . 1-1 CPU Data Flow . . . . . . . . . . . . . 1-9 Arithmetic Operations . . . . . . . . . 1-13 Fixed Point Arithmetic. . . . . . . . 1-13 Packed Decimal Arithmetic . . . . . 1-16 IBM System/360 General Information. . 1-25 Basic Programming . . . . . . . . . 1-41 Storage Protection. . . . . . . . . . 1-70 Programming Systems . . . . . . . . . . . . 1-74 CHAPTER 2. FUNCTIONAL UNITS. . . . . 2-1 Read Only Storage and Microprogram. . 2-4 Arithmetical Logical Unit (ALU) . . . 2-52 CHAPTER 3. PRINCIPLES OF OPERATION . 3-1 Instruction Read-In . . . . . . . . 3-1 ROS Timing to Core Storage Timing . . 3-1 Break-In-Timings. . . . . . . . . . . . . . . . . 3-3 Branch on Condition (RR Format) . . . 3-17

## List of Abbreviations

| ALU<br>ASCII<br>Aux Stor | Arithmetic Logic Unit<br>American Standards Code for<br>Information Interchange<br>Auxiliary Storage |

|--------------------------|------------------------------------------------------------------------------------------------------|

| BCD                      | Binary Coded Decimal                                                                                 |

| bin                      | binary                                                                                               |

| CAW<br>CID               | Channel Address Word<br>Compatibility Initialization<br>Deck                                         |

| CLD                      | CAS Logic Diagram                                                                                    |

| CPU                      | Central Processing Unit                                                                              |

| CROS                     | Capacitor Read Only Storage                                                                          |

| CU                       | Control Unit                                                                                         |

| dec                      | decimal                                                                                              |

| EBCDI<br>EOF             | Extended Binary Coded Decimal<br>Interchange<br>End of File                                          |

| GM                       | Group Mark                                                                                           |

| GMWM                     | Group Mark Word Mark                                                                                 |

| IC                       | Instruction Counter                                                                                  |

| I/O                      | Input-Output                                                                                         |

| IPL                      | Initial Program Loader                                                                               |

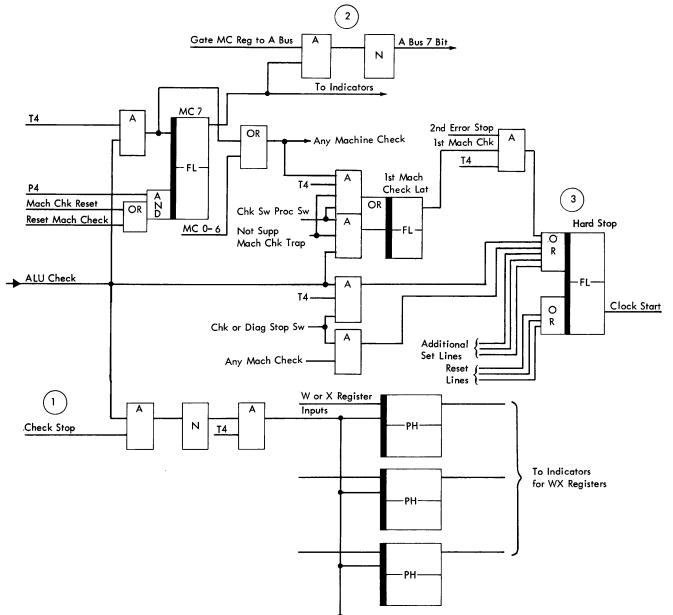

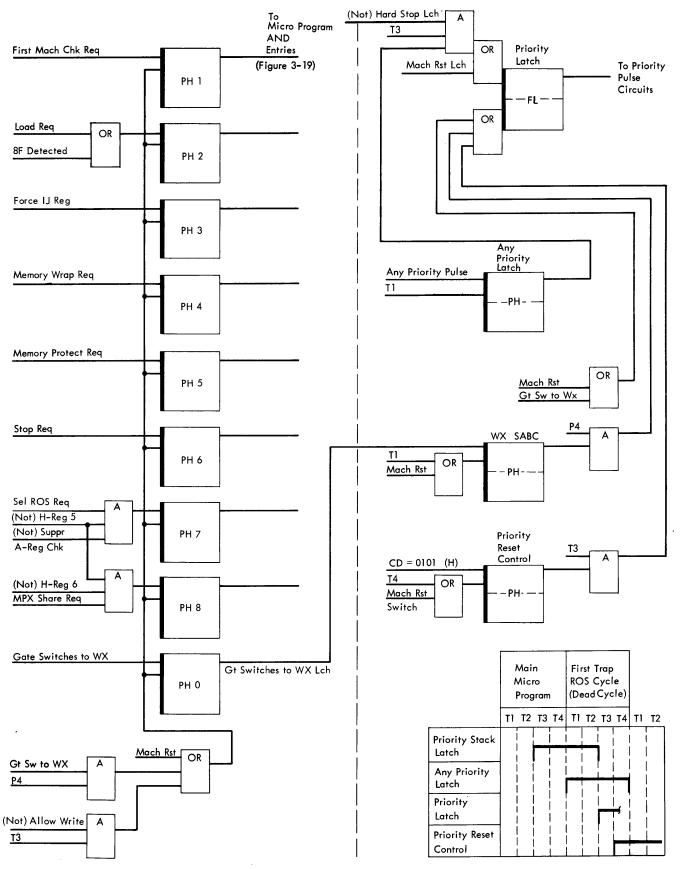

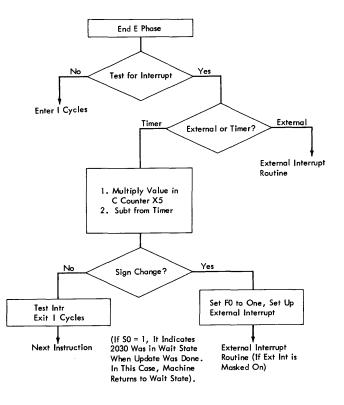

| Machine Check Microprogram<br>Forced Microprogram Entries<br>Parity Check Timings                                       | •           | 3-41                                |

|-------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|

| CHAPTER 4. FEATURES                                                                                                     | •           | 4-1                                 |

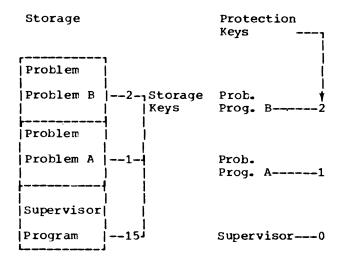

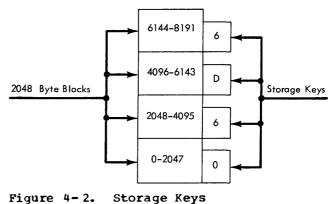

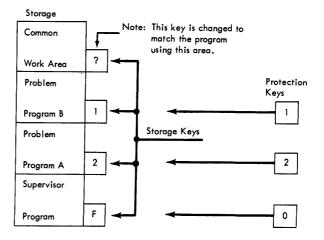

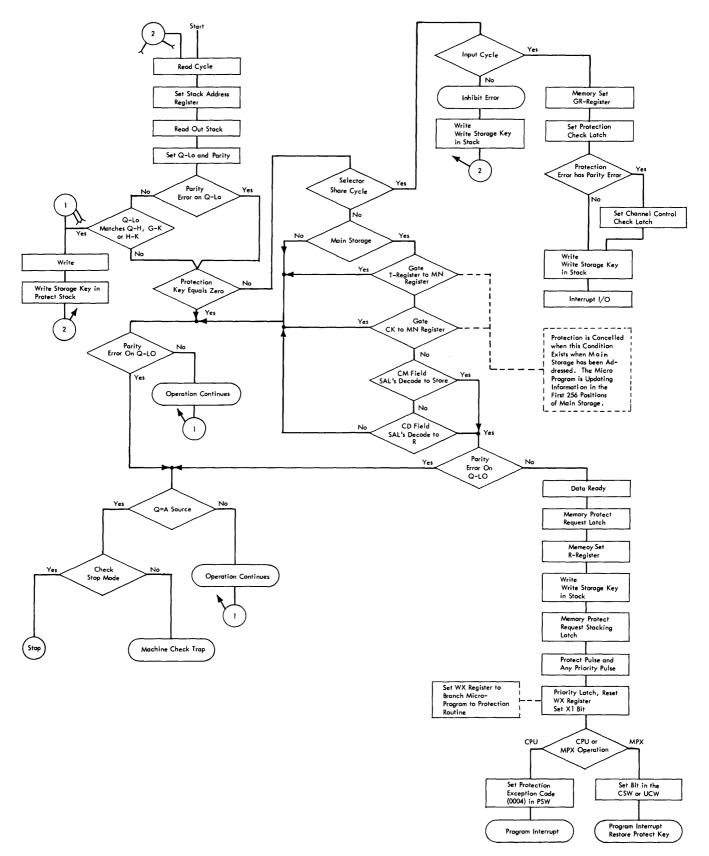

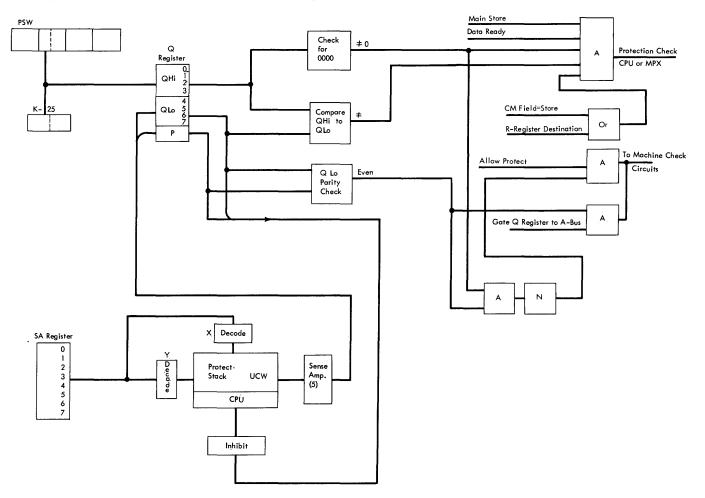

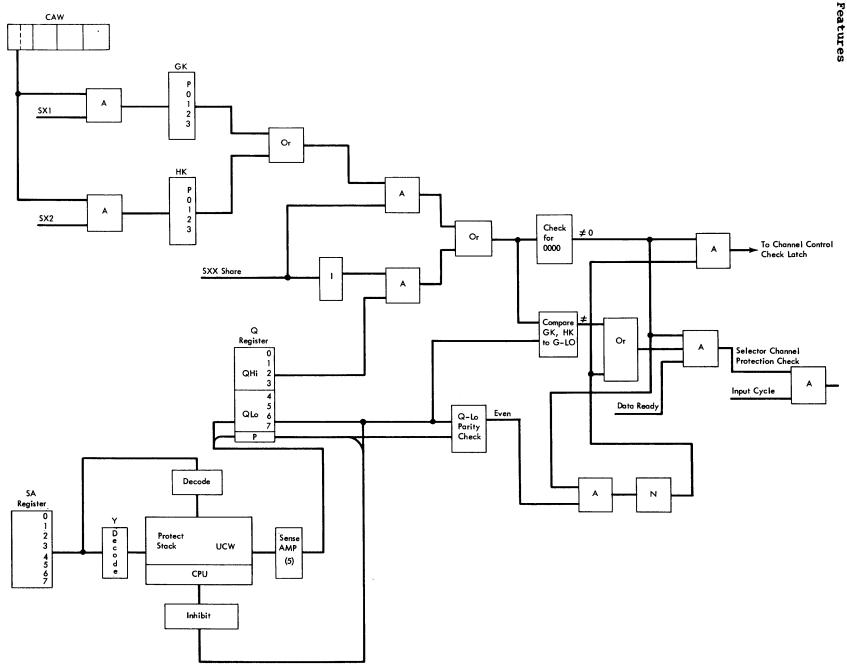

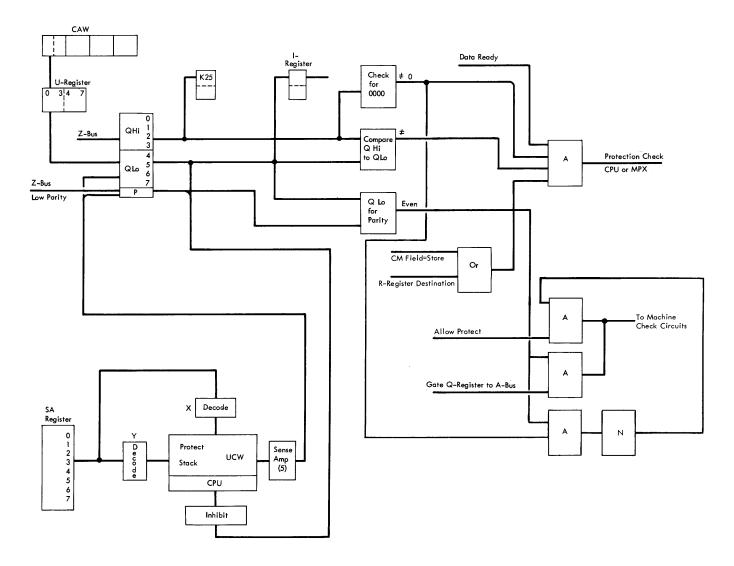

| Storage Protection                                                                                                      | •<br>•<br>• | 4-25<br>4-28<br>4-75                |

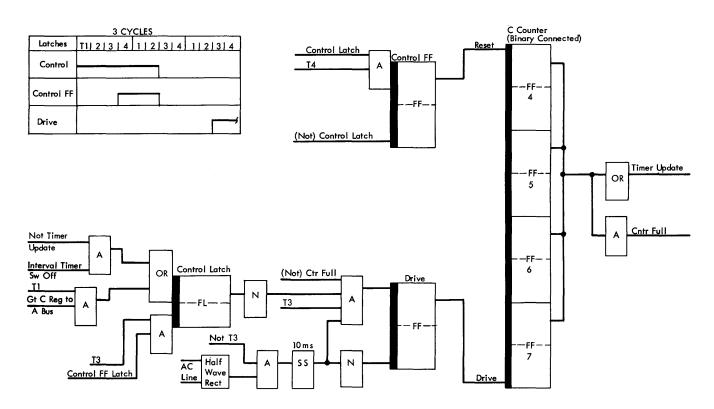

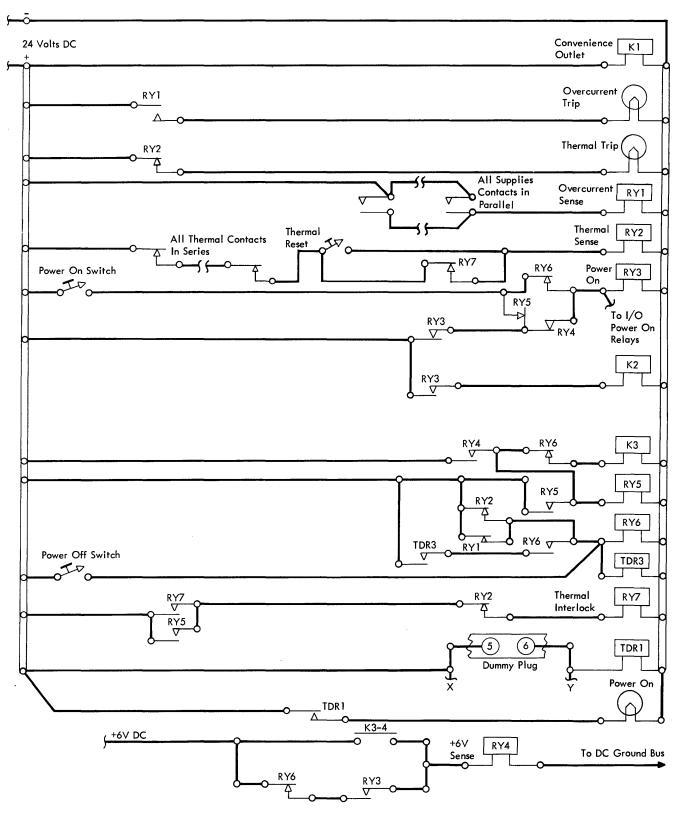

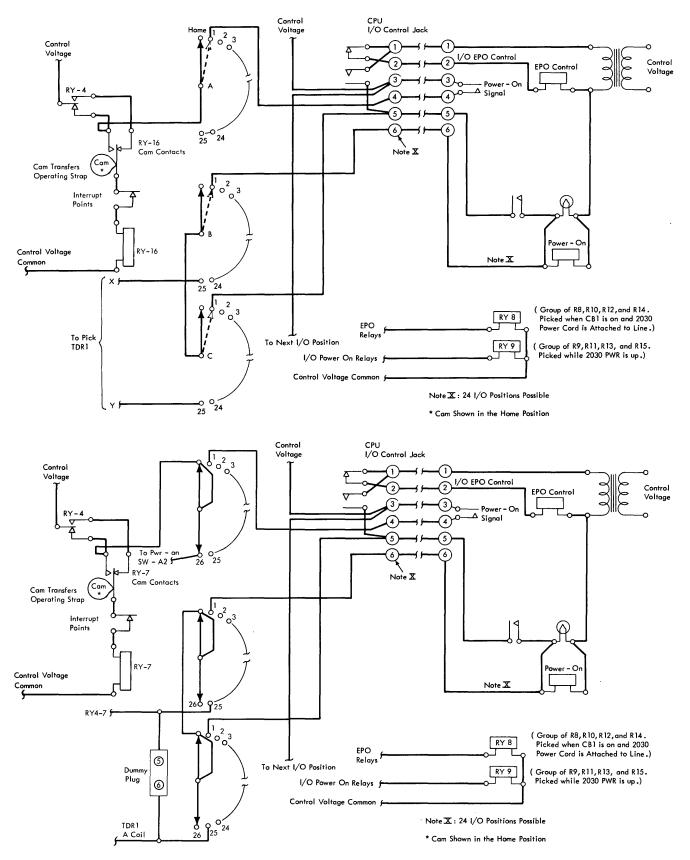

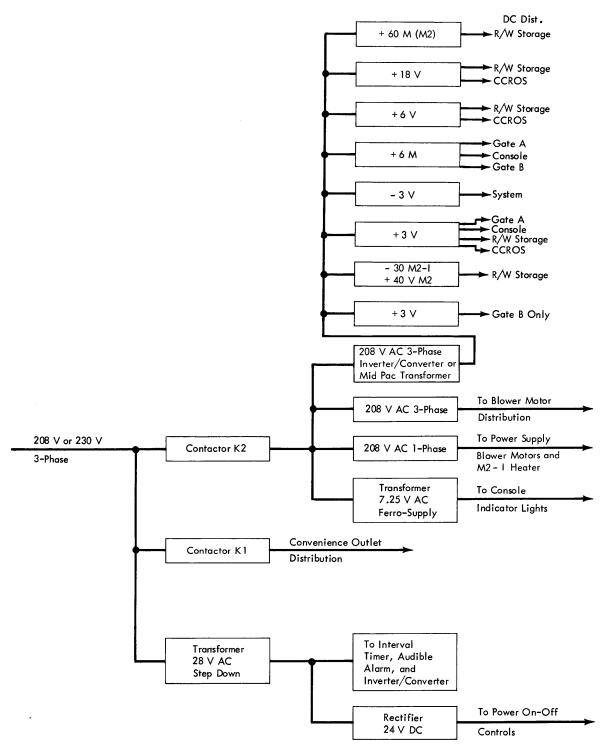

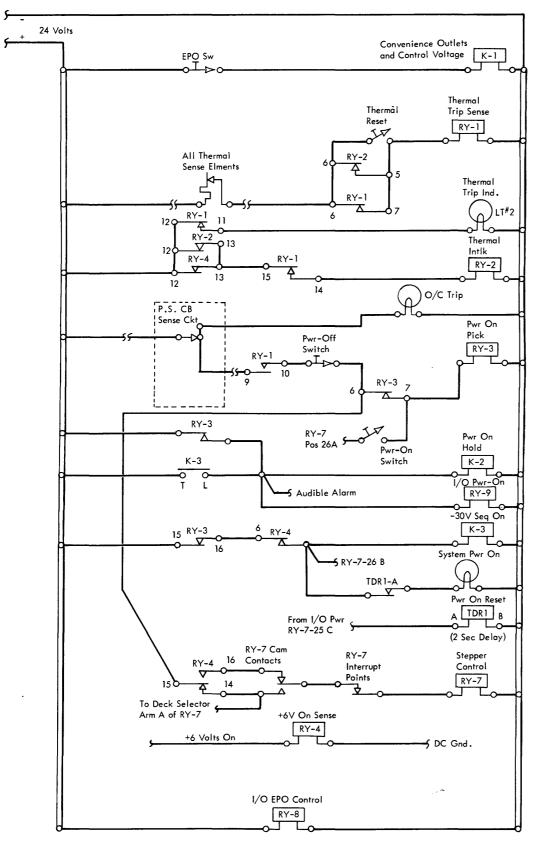

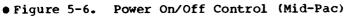

| CHAPTER 5. POWER SUPPLIES                                                                                               | •           | 5-1                                 |

| Power-On Sequence (Stepper Switch).<br>Power-Off Sequence<br>Power-On Sequence (Mid-Pac)<br>Power-Off Sequence (Mid-Pac | •           | 5-1<br>5-5<br>5-7<br>5-7            |

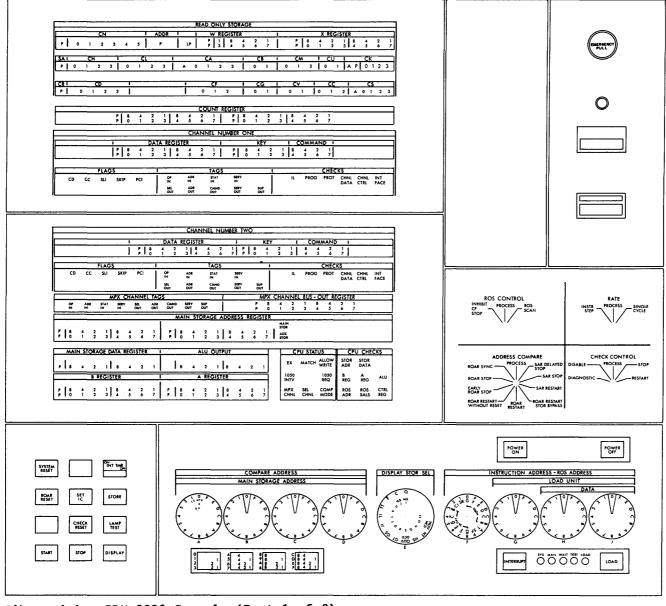

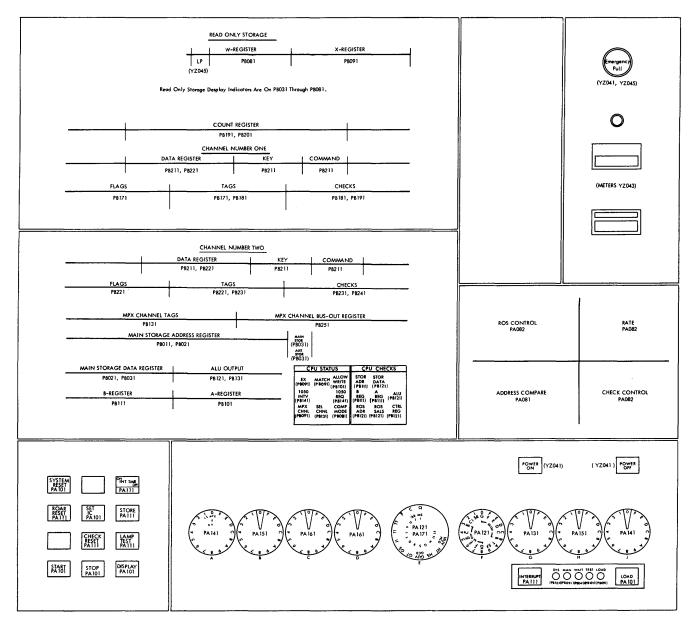

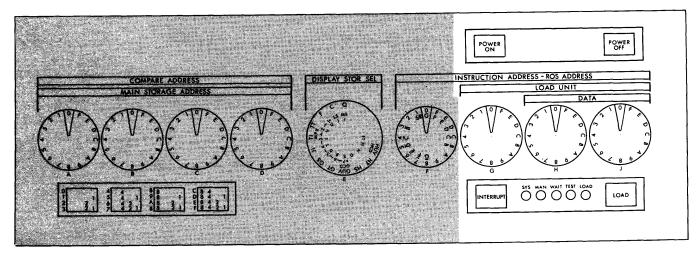

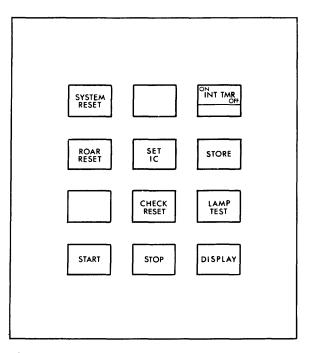

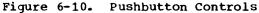

| CHAPTER 6. CONSOLE AND MAINTENANCE<br>FEATURES                                                                          | •           | 6-1                                 |

| 2030 Console                                                                                                            |             | 6-9<br>6-13<br>6-14<br>6-15<br>6-16 |

| APPENDIX A                                                                                                              | •           | A-1                                 |

| APPENDIX B                                                                                                              | •           | A-3                                 |

| INDEX                                                                                                                   |             | V. 1                                |

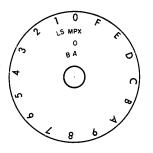

| L<br>LS   | length code<br>Local Storage |

|-----------|------------------------------|

| MPX<br>MS | Multiplexor<br>main storage  |

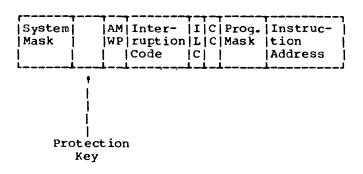

| PSW       | Program Status Word          |

| RBC       | Read Back Check              |

| ROAR      | Read Only Address Register   |

| ROS       |                              |

| RPG       | Report Program Generator     |

| RR        | Register-to-register         |

| RS        | Storage-to-register          |

| RX        | Storage-to-register          |

| SA        | Stack Address                |

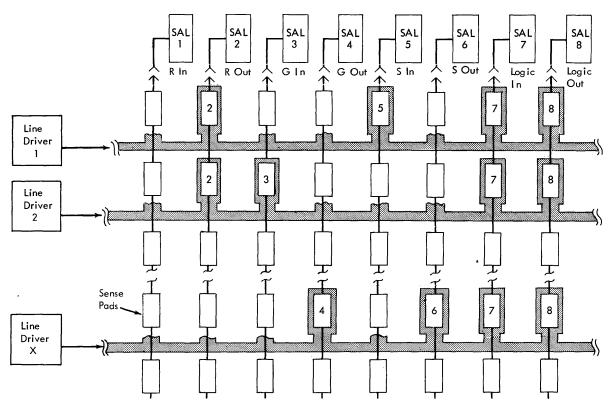

| SAL       | Sense Amplifier Latch        |

| SI        | Storage-immediate            |

| SLD       | Simplified Logic Diagram     |

| SRL       | System Reference Library     |

| SS        | Storage-to-storage           |

|           |                              |

UCW Unit Control Word

```

WLR Wrong Length Record

WM Word Mark

```

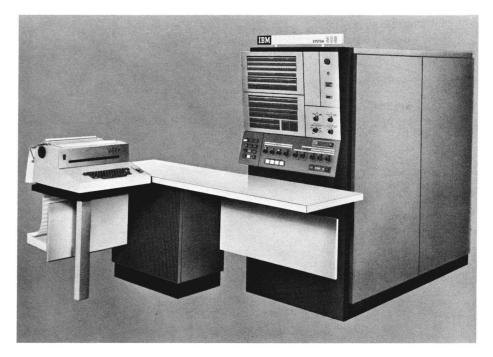

Figure 1-1. IBM System/360 Model 30 with IBM 1052 Documentary Console

CHAPTER 1. INTRODUCTION

The first part of this chapter is an introduction to IBM System/360 Model 30 characteristics. Basic System/360 information (such as data formats and basic programming concepts) is subsequently described in the <u>IBM System/360 General Information</u> section of this chapter. The material in this general information section covers many of the topics included in the Field Engineering System/360 Introductory Programming

Student Self-Study Course. (The self-study course is a prerequisite to this publication.) The general information section is primarily for reference and review purposes.

The last part of Chapter 1 is an introduction to certain programming systems concepts with which you should be familiar.

### OVERALL DATA FLOW

- Overall control of system operations is provided by control circuitry that interprets instructions and regulates the actions called for by instructions.

- Three basic areas controlled are:

- 1. The arithmetic logic unit (ALU)

- 2. Core storage

- 3. Channels

- A channel is a control and data link between I/O control units and the processing unit.

- An I/O control unit responds to the channel in a standard way over the standard I/O interface cable.

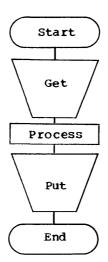

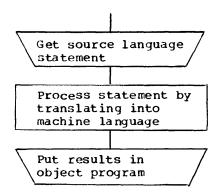

Any data processing system performs three basic operations:

- Information is entered into the system by use of an input device, such as a card reader.

- The input information is processed. (Processing includes arithmetical and logical manipulations of source information. The processed information is then usually put into some predetermined format.)

- 3. The formatted information is sent to an output device, such as a printer or card punch, which then produces a mean-ingful record of the processed information.

Control of these input, arithmetic, logic, and output functions must be provided. This control is achieved by interaction of two factors:

A series of instructions (program) that indicates the operations to be performed. 2. Machine control circuitry that is capable of interpreting and then directing performance of the operations called for by the program.

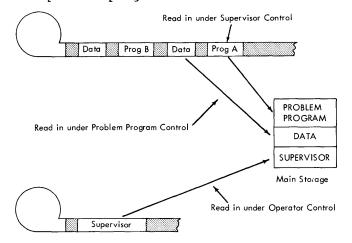

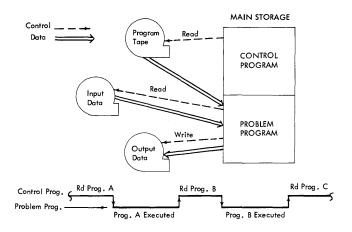

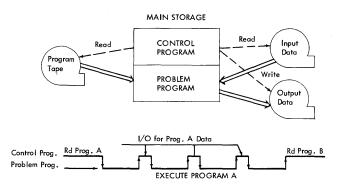

Because speed is an important factor, each instruction must be obtained quickly by the machine. In System/360 Model 30, the program controlling the system is located in high-speed main storage. (How a program is initially put into main storage is not pertinent to this discussion.)

The control circuitry of the system interprets an instruction fetched from main storage and directs performance of the indicated operation. The next instruction is then obtained from storage and its operation is performed. This sequence is repeated until the job is completed or terminated at an intermediate step.

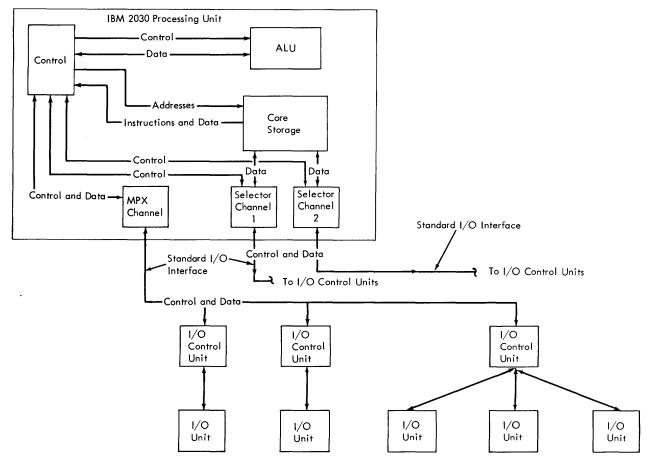

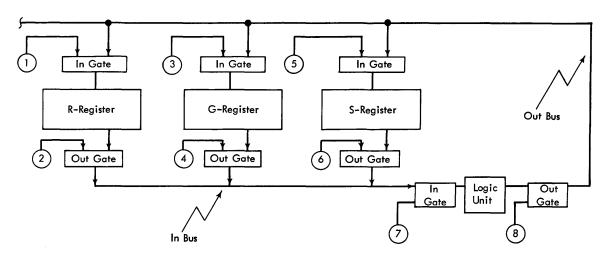

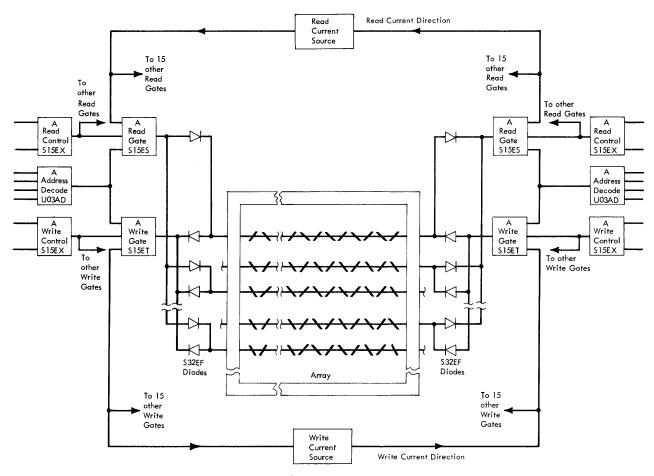

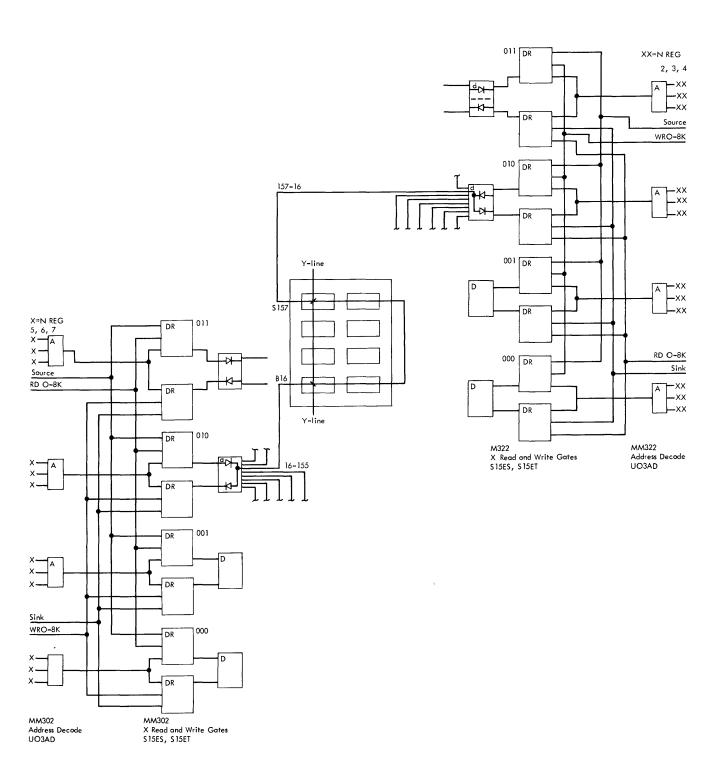

In the System/360 Model 30, during the processing of any instruction, one (or two, or all three) of three basic areas must be controlled. (Figure 1-2):

1. The ALU (Arithmetic Logic Unit) in

which arithmetical and logical manipulations of information are performed.

- Core storage, either (or both) main storage or an auxiliary storage (that contains, among other things, areas devoted to general registers, floating point registers, and certain controlling information for I/O operations).

- Channels, which are the main controlling elements in I/O operations (which, in general, take precedence over non-I/O operations).

Notice in Figure 1-2 that any input/output channel is a link between I/O control units and the control circuitry in the IBM 2030 (the processing unit for System/360 Model 30). A CU (Control Unit) is necessary for the operation of any I/O device attached to the System/360 Model 30. The CU may be an integral part of an I/O unit or it may be a separate unit to which the I/O device is attached. In either case, the CU has circuitry that allows it to communicate with a channel. The data and control information exchanged between a channel and any CU is in a standard form; therefore, a channel can communicate with any CU as long as the circuitry in the CU is able to operate through the use of the standard signals recognized by the channel. A cable that connects CU's with a channel is called a standard I/O interface cable.

Note, however, one exeption: The 1050 Documentary Console is not attached, on the Model 30, to a standard I/O interface cable.

Figure 1-2. System/360 Model 30 Overall Data Flow

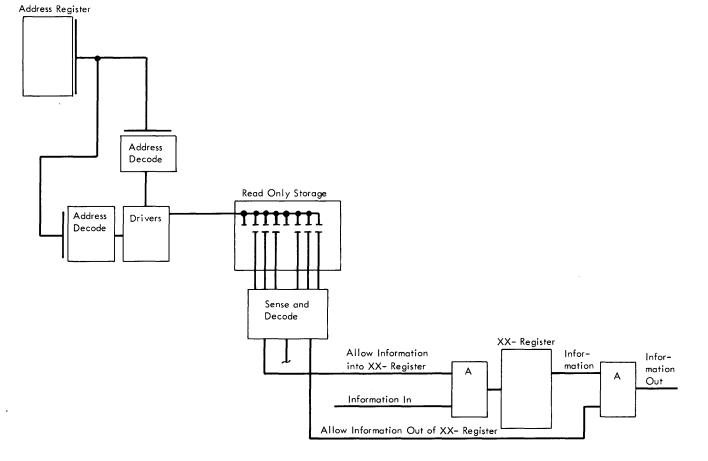

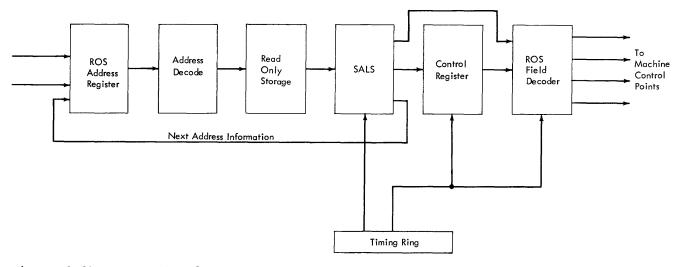

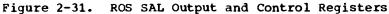

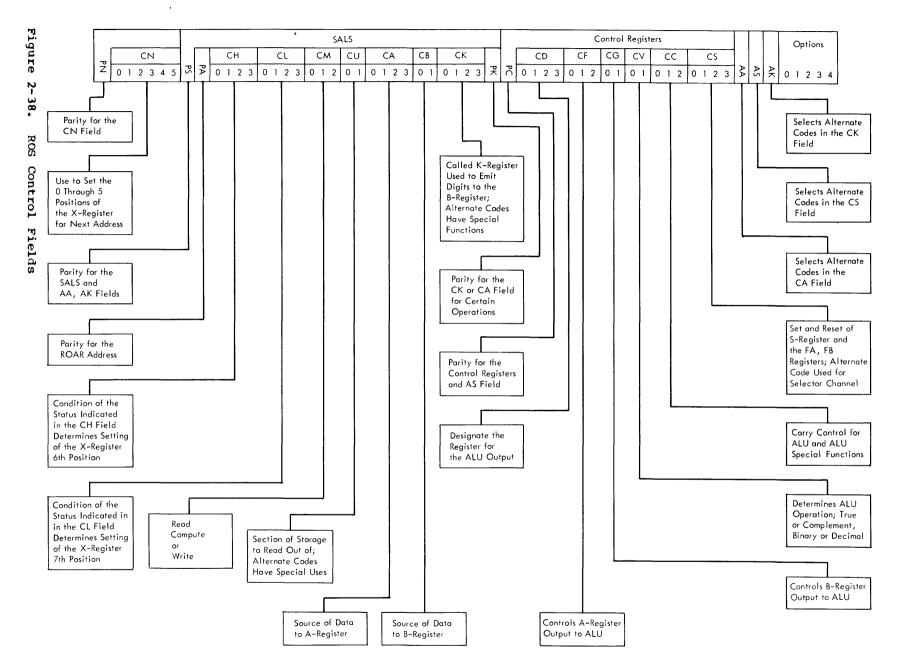

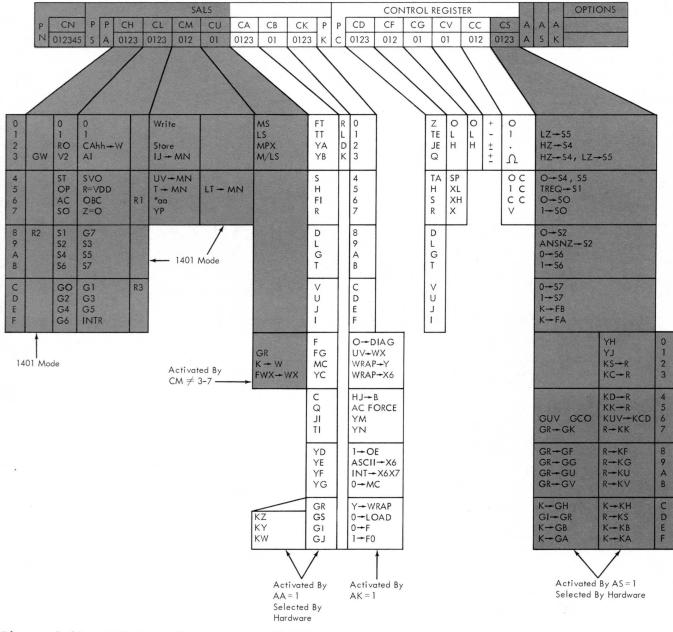

### ROS (READ-ONLY-STORAGE) CONTROL

• Read-only-storage (ROS) is the basic <u>control</u> circuitry for System/360 Model 30.

Control circuitry is the guiding or regulating medium of the system. There are, however, various levels of control. For example, suppose that a specific byte is to be read out of main storage. To read out the specified byte, the following actions occur:

- 1. The address of the byte is set into storage address registers.

- 2. The output of these registers is used to specify the storage location.

- 3. The byte is read out of storage and placed into a machine register.

In a sense, the outputs of the storage address registers control addressing of storage. However, the storage address registers themselves are controlled by ROS, both when the address is initially set into them, and when it is read out.

In System/360 Model 30, basic controlling circuitry is called ROS (Read-Only-Storage). Outputs of ROS circuitry determine which circuit elements (such as registers) are used and how they are used for each operation. For information about the functions and physical makeup of ROS, refer to <u>Chapter 2</u> of this publication.

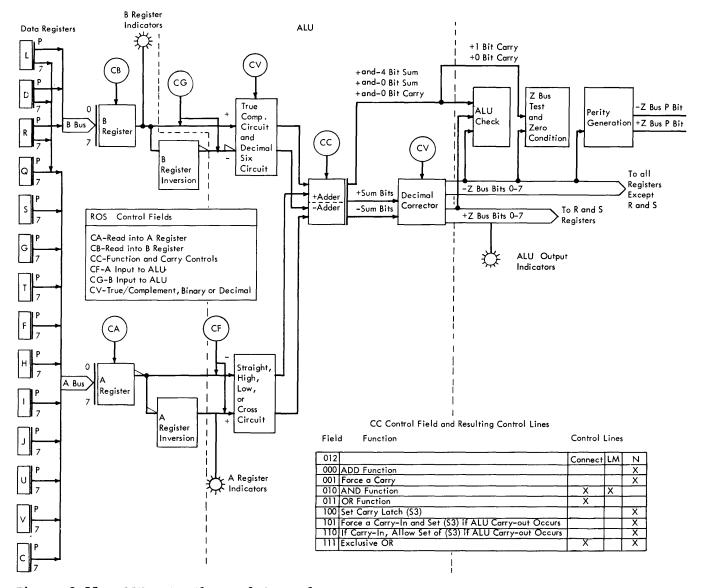

ALU (ARITHMETIC LOGIC UNIT)

- Arithmetic and logical operations are performed on binary and packed decimal data (if decimal feature is used) by the ALU.

- Two registers (B and A) provide input to the ALU.

- Control circuitry (ROS) directs, as indicated by an instruction, both the operation to be performed by ALU and how the data in the B- and A-registers is to be used by ALU.

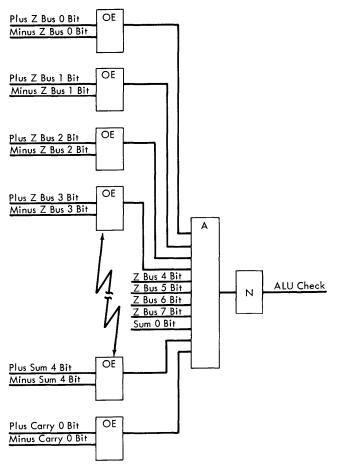

- Parity is not carried through the ALU circuits. Correct parity is generated for the resulting byte after the information has passed through the ALU.

- Data is sent through the ALU in both true and complemented form, thereby providing a check of ALU operations.

## The ALU performs:

- 1. Arithmetic operations of:

- a. Adding and

- b. Subtracting.

- 2. Logical operations of:

- a. ANDing,

- b. ORing, and

- c. Exclusive ORing.

The ALU performs binary addition and subtraction (i.e., complement addition) on fixed-point data, two bytes (one from each operand) at a time. If the decimal feature is used, additions and subtractions are performed on packed decimal operands. Here, each byte contains two packed decimal digits; one digit is in the four high-order bits, and the other in the four low-order bits. (The sign is carried in the four low-order bits of the low-order byte.) A packed decimal digit is valid only if the four bits that represent it are in the range 0000 to 1001 (binary).

Two registers (the B- and A-registers) provide the basic information-inputs to ALU. The original information set into these two registers can come from a variety of sources. The sources used depend upon the operation performed.

- ROS output:

- Controls the manner in which the contents of the B- and A-registers are

sent to ALU. (Some ALU operations do not require use of two full bytes of data. For example, comparison against four bits of a mask field requires only two separate four bit entries into ALU.)

Specifies the type of operation to be performed (true or complement, binary or decimal, add, AND, OR, exclusive OR) as indicated by the instruction being processed. Parity is not carried through ALU circuitry. Input line levels are complemented so that input to ALU is in both true and complemented form. Exclusive OR circuitry is used to check that each output line at an up level has a corresponding complemented line at a down level. Correct parity for the result byte is generated after the data has passed through ALU.

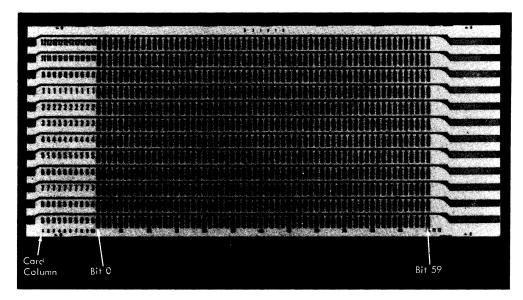

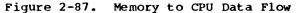

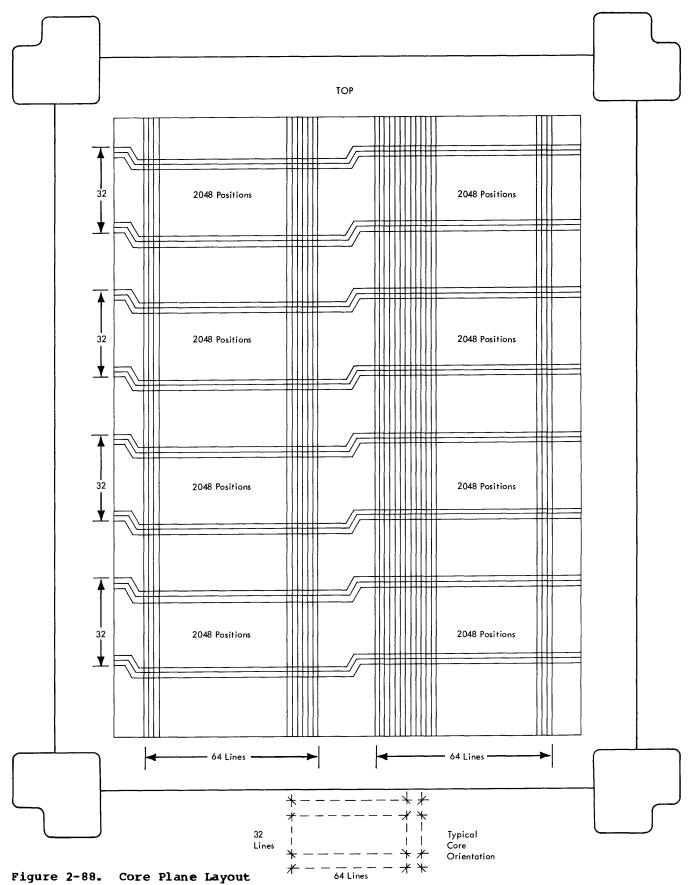

STORAGE SIZES AND CYCLE TIMES

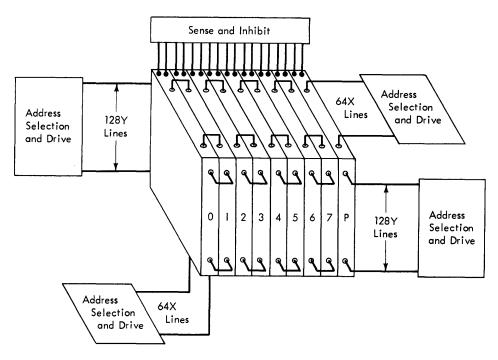

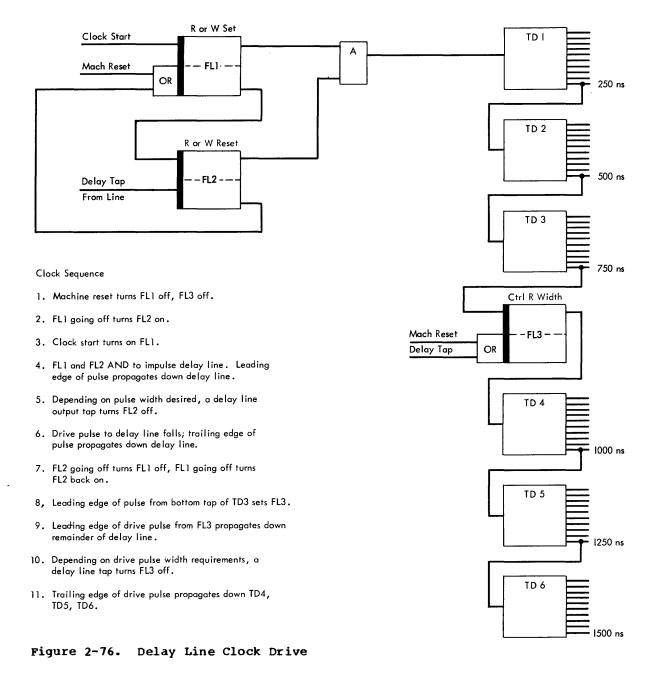

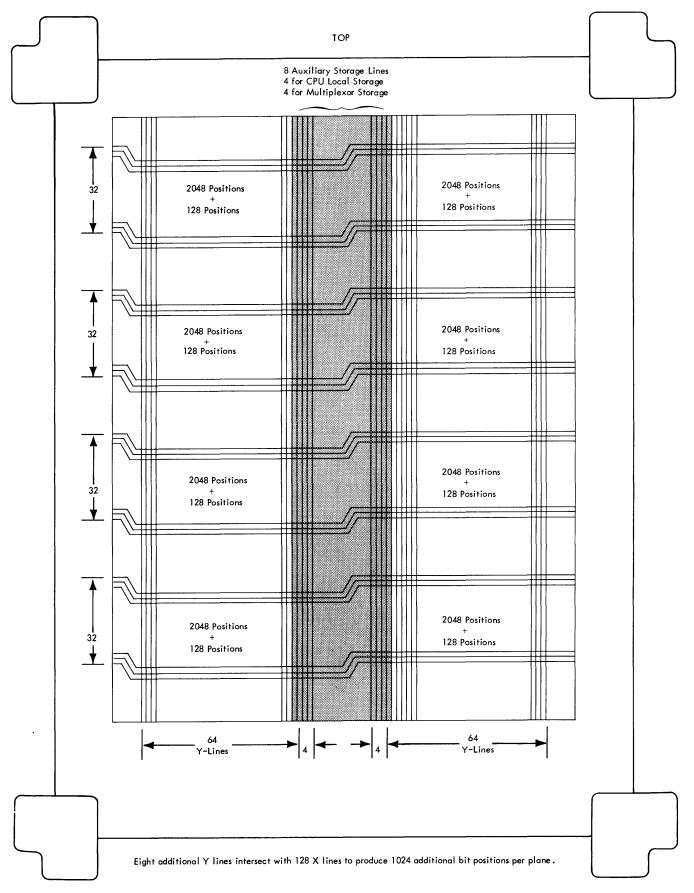

- Model 30 uses <u>either</u> a 1.5 <u>or</u> a 2.0 microsecond storage cycle (i.e., read/write cycle).

- Information is handled one byte at a time in System/360 Model 30 core storage.

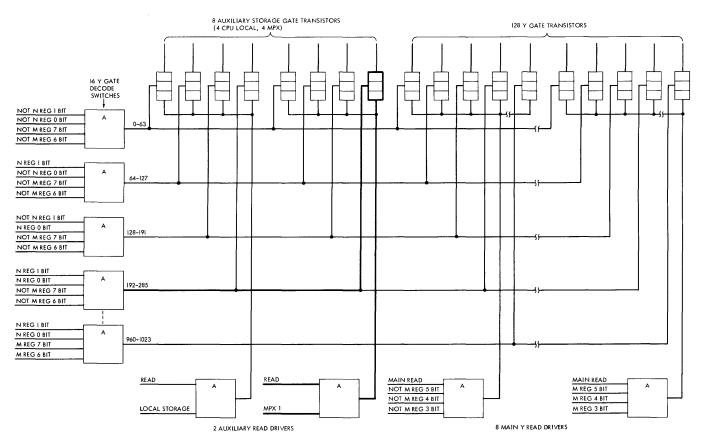

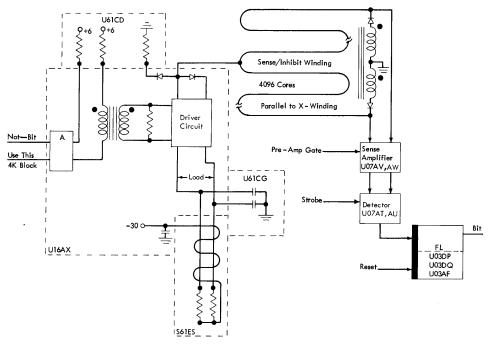

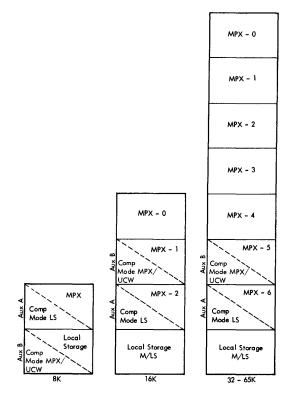

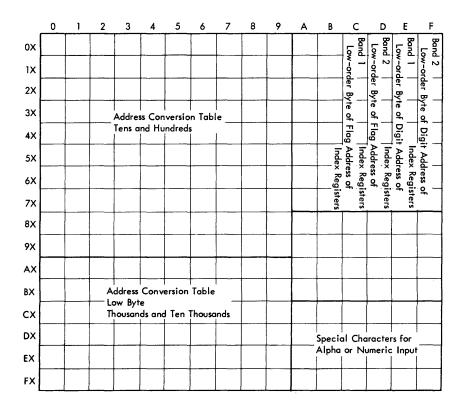

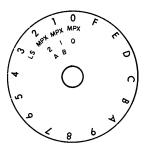

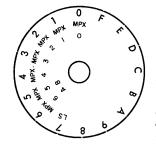

- Auxiliary storage is made up of local storage and MPX (multiplexor) storage.

- The sixteen general registers and the four floating point registers are in local storage.

- MPX storage contains the multiplexor channel's Unit Control Words.

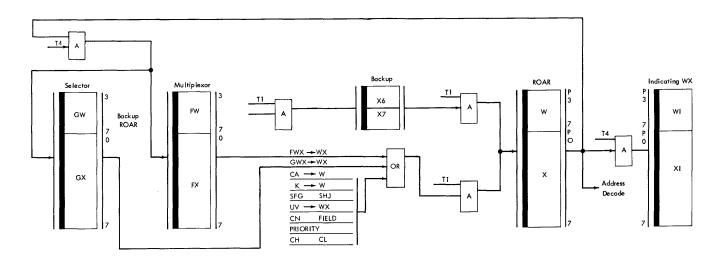

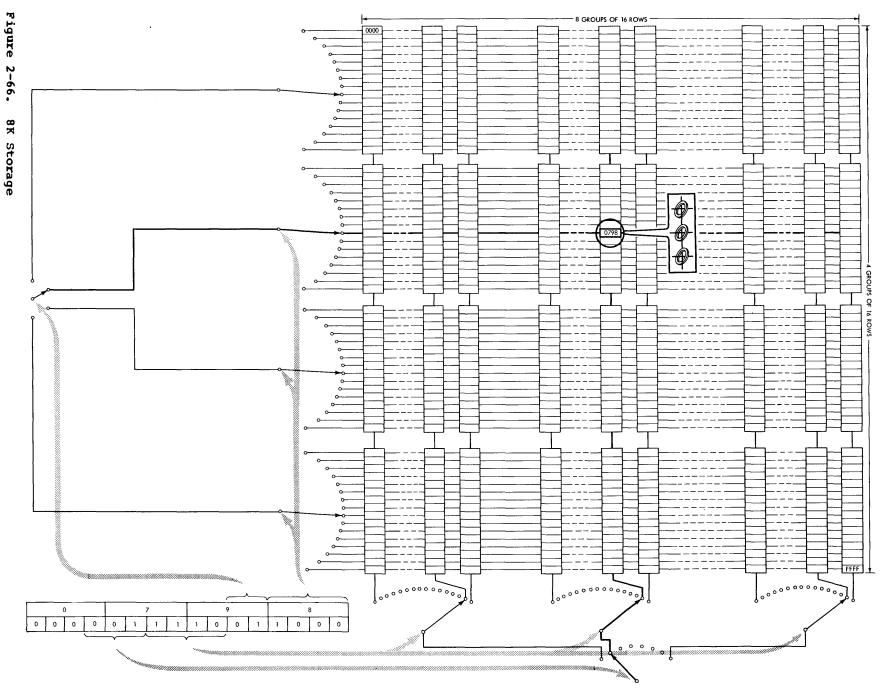

The IBM 2030 Processing Unit contains core storage and logic, arithmetic, and control circuits for IBM System/360 Model 30. Four models are available; the primary characteristic of each model is its amount of main storage. The letter prefix in the model designation indicates the amount of main storage:

## System/360 Model Main Storage (in bytes)

| C30  | 8192  |

|------|-------|

| D30  | 16384 |

| E 30 | 32768 |

| F30  | 65536 |

Each one of the four models has either (but not both) a 1.5- or a 2.0-microsecond storage cycle (such as read from and then immediately write into storage).

Refer to the Data Width column in Figure 1-3 or Figure 1-4. Notice that one byte (eight bits plus parity) at a time is handled in Model 30. This is true for the general and floating point registers as well as for main storage. Handling a word (four bytes) in a general register requires at least 6 microseconds in the 1.5-microsecond storage cycle system (Figure 1-3). What is meant here is that one byte at a time is read from a general register and then written, for example, into a main storage location. Other operations, such as computations, may extend the time, but to read and write in succession requires at least 1.5 microseconds per byte. (Other models of System/360 [Model 40, Model 50, etc.] handle more than one byte per storage access cycle.)

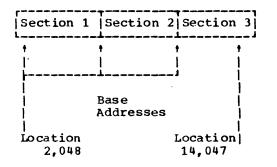

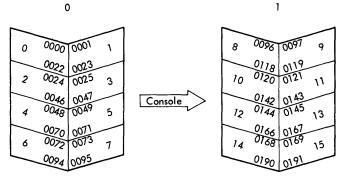

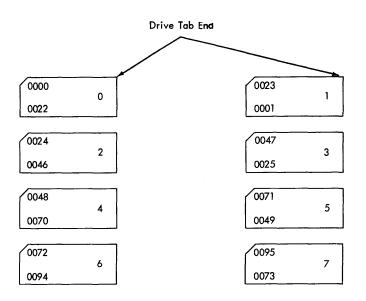

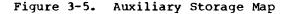

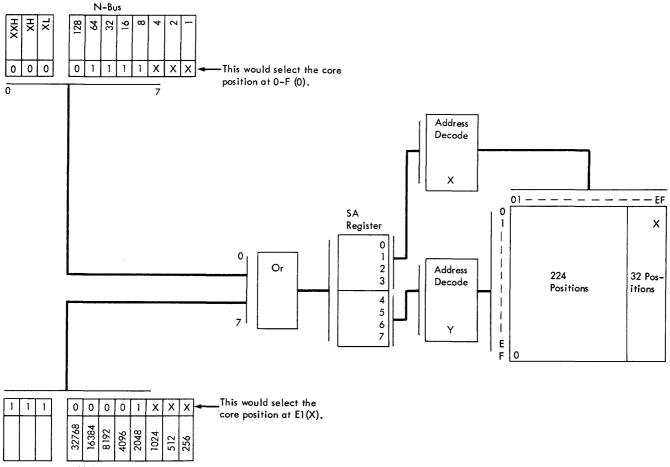

An additional core storage area, called auxiliary storage, is contained in the 2030 (Figure 1-5). Auxiliary storage is a part of the main storage array. However, auxiliary storage is addressed differently and does not use any of the main storage locations. The amount of available auxiliary storage is, in general, dependent upon the size of the main storage array. Standard auxiliary storage capacity for each model is:

| Model | Auxiliary Storage (bytes) |

|-------|---------------------------|

| C30   | 512                       |

| D30   | 1024                      |

| E30   | 1024                      |

| F30   | 1024                      |

Auxiliary storage is made up of two areas:

Local storage, and MPX (Multiplexor) storage.

Local storage contains the sixteen general registers, the four floating point registers, and other miscellaneous areas. Every Model 30 has 256 bytes of local storage.

| Characteristics                            | Speed<br>(in microseconds) | Data Width<br>Bits (Bytes) |

|--------------------------------------------|----------------------------|----------------------------|

| Basic Machine Cycle                        | .75                        |                            |

| Main Storage:                              | 1.5                        | 8 (1)                      |

| Model C30 8192 Bytes                       |                            |                            |

| Model D30 16384 Bytes                      |                            |                            |

| Model E30 32768 Bytes                      |                            |                            |

| Model F30 65536 Bytes                      |                            |                            |

| Registers Accessible to<br>Programmer:     |                            |                            |

| Sixteen General Registers *                | 6                          | 32 (4)                     |

| Four Floating–Point Registers *            | 12                         | 64 (8) Double<br>Precision |

|                                            | 6                          | 32 (4) Single<br>Precision |

| System Control:<br>Read Only Storage (ROS) | .75                        |                            |

\* These registers are in local storage (a storage area that is in addition to the main storage capacity).

# Figure 1-3. CPU Characteristics

The remainder of auxiliary storage is used to contain multiplexor channel UCW's (Unit Control Words). Each one of these UCW's contains the information necessary to control the I/O unit, on the multiplexor channel, to which the UCW pertains. There are 32 UCW's, each eight bytes long, in the MPX storage of Model C30. Hence, a maximum of 32 subchannels can be controlled from information in MPX storage in Model C30. Models D30, E30, and F30 can use up to 96 UCW's in MPX storage as a standard feature. Models E30 and F30, however, can have the Additional Multiplexor Subchannels optional feature that allows use of up to 224 sub-channels. (If this feature is installed, 2048 bytes are used for auxiliary storage.) If the 1400 or 1620 compatibility feature is installed, certain parts of MPX storage are used for purposes other than storing UCW's.

| Characteristics                            | Speed<br>(in microseconds) | Data Width<br>Bits (Bytes) |

|--------------------------------------------|----------------------------|----------------------------|

| Basic Machine Cycle                        | 1                          |                            |

| Main Storage:                              | 2                          | 8 (1)                      |

| Model C30 8192 Bytes                       |                            |                            |

| Model D30 16384 Bytes                      |                            |                            |

| Model E30 32768 Bytes                      |                            |                            |

| Model F30 65536 Bytes                      |                            |                            |

| Registers Accessible to<br>Programmer      |                            |                            |

| Sixteen General Registers *                | 8                          | 32 (4)                     |

| Four Floating-Point Registers *            | 16                         | 64 (8) Double<br>Precision |

|                                            | 8                          | 32 (4) Single<br>Precision |

| System Control:<br>Read Only Storage (ROS) | 1                          |                            |

\* These registers are in local storage (a storage area that is in addition to the main storage capacity).

# Figure 1-4. CPU Characteristics (2.0 Microsecond Read/Write Cycle)

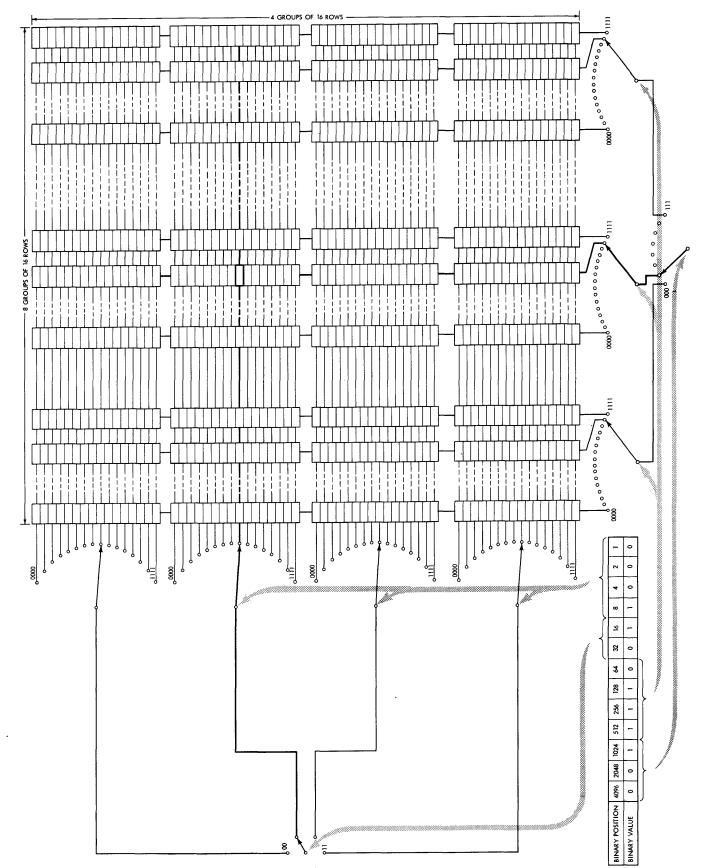

Core Storage Array

| Main Storage                                                   |                                                          |                      |  |  |  |  |  |  |

|----------------------------------------------------------------|----------------------------------------------------------|----------------------|--|--|--|--|--|--|

| Model                                                          | Capa                                                     | Capacity ( in Bytes) |  |  |  |  |  |  |

| C30                                                            | 8                                                        | 3,192                |  |  |  |  |  |  |

| D30                                                            | 10                                                       | 5,384                |  |  |  |  |  |  |

| E30                                                            | 32                                                       | 2,768                |  |  |  |  |  |  |

| F30                                                            | 65,536                                                   |                      |  |  |  |  |  |  |

| Auxiliary Storage                                              |                                                          |                      |  |  |  |  |  |  |

| Local Storage                                                  | M                                                        | PX Storage           |  |  |  |  |  |  |

| 256 Bytes in Every System/360                                  | Model                                                    | Number of UCWs       |  |  |  |  |  |  |

| Model 30                                                       | C30                                                      | 32                   |  |  |  |  |  |  |

|                                                                | D30                                                      | 96                   |  |  |  |  |  |  |

| (Contains 16 general purpose                                   | E30                                                      | 96*                  |  |  |  |  |  |  |

| registers, 4 floating point<br>registers, and other miscellan- | F30                                                      | 96*                  |  |  |  |  |  |  |

| eous areas.)                                                   | * Model E30 or F30 can have                              |                      |  |  |  |  |  |  |

|                                                                | 224 UCWs if the Additional                               |                      |  |  |  |  |  |  |

|                                                                |                                                          |                      |  |  |  |  |  |  |

|                                                                | Multiplexor Subchannels<br>Optional feature is installed |                      |  |  |  |  |  |  |

|                                                                |                                                          | arore is installed   |  |  |  |  |  |  |

Figure 1-5. Core Storage Allocations

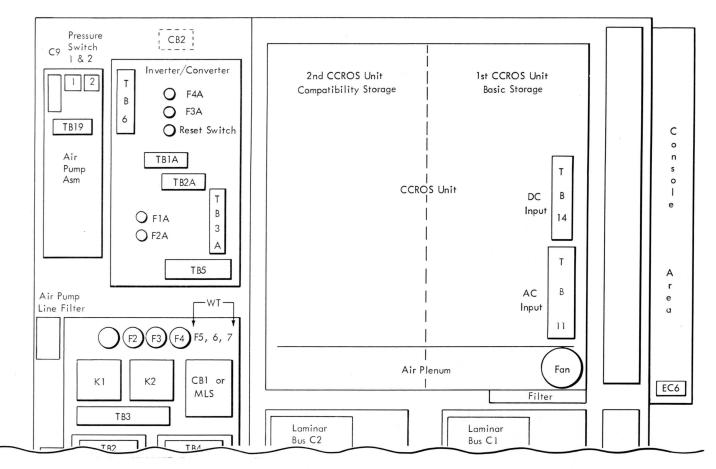

### CHANNELS

- Up to three channels can be installed in System/360 Model 30:

- 1. One Multiplexor Channel

- 2. Selector Channel 1

- 3. Selector Channel 2

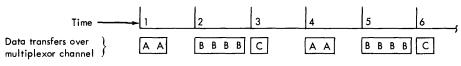

- The multiplexor channel can operate in either multiplex or burst mode; a selector channel operates only in burst mode.

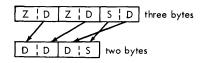

Key:

- B Data bytes to device B from main storage.

- C Data byte from device C to main storage

Figure 1-6. Multiplex Mode Operation

The 2030 can have up to three channels:

- 1. A multiplexor channel (standard feature)

- 2. Selector Channel 1 (special feature)

- 3. Selector Channel 2 (special feature)

The main purpose of the multiplexor channel is to provide for operation of lower speed I/O devices in multiplex (data interleaved) mode (Figure 1-6). In the multiplex mode, information is transferred in groups of bytes between the processing unit and several I/O devices concurrently. For example, multiplexing service for two serial unbuffered card readers could proceed as follows:

- One byte of data is sent from the control unit of the first card reader to the processing unit.

- Next, one byte of data is sent from the control unit of the second card reader to the processing unit.

Steps 1 and 2 are repeated until a complete record is transferred for one of the units.

Servicing for the other unit is then completed alone.

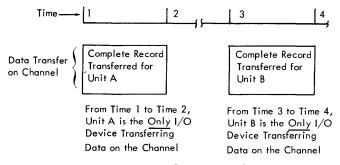

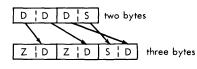

While some I/O units always operate in burst mode regardless of the channel, buffered units (except the 2520) attached to the multiplexor channel can operate in burst mode as well as in multiplex mode. This capability is provided by a switch associated with the buffered unit. In burst mode (Figure 1-7), the data transfer is completed on a record basis.

Multiplexing operations are not allowed on the multiplexor channel during the time that a unit attached to the multiplexor channel is operating in burst mode. Therefore, a burst mode unit should not be started (on the multiplexor channel) while units that are multiplexed are operating.

Selector channels operate only in burst mode. An I/O control unit obtains control of the channel and transfers an entire record (i.e., multiplexing does not occur) for the associated I/O unit. After the record is transferred (and if no chaining for the same unit occurs), another I/O control unit can obtain control of the selector channel for record transfer.

A Data byte from device A to main storage.

Figure 1-7. Burst Mode Operation

# Multiplexor Channel

- Some of the CPU circuits are used by the multiplexor channel for its operations.

- Certain information used in CPU instruction processing is stored in local storage during multiplexor channel operations.

- UCW information is used to indicate how an I/O unit's operation is controlled on the multiplexor channel.

- The maximum number of I/O units that can be addressed on the multiplexor channel is dependent upon:

- 1. The amount of MPX storage available.

- 2. The number of shared subchannels used.

- 3. The fact that a maximum of eight CU's can be attached to the standard I/O interface cable.

The terms "concurrent", "simultaneous", and "multiplex" are used consistently in System/360 publications. What, however, is meant by these terms when applied to System/360 Model 30 multiplexor channel operations? Consider a typical multiplexor channel data transfer.

In the 2030, certain CPU circuits are shared with the multiplexor channel. Therefore, CPU instruction processing operations are stopped during the time that a multiplexor channel operation (data transfer or chaining) is in progress. Assume that an add operation is being executed in the CPU and that a 1442 card read operation is in progress. CPU control circuitry, including certain registers (not the 16 general or 4 floating point registers), contains information that is updated as the add instruction is executed. Now suppose that the I/O CU (Control Unit) of the 1442 requests channel service (i.e., the CU has a data byte ready for transfer to storage). The CU can wait to transfer the data byte for only a certain time period. This time

is dependent upon when the next card column is read. If the first byte is not transferred before the next byte is ready, data is temporarily lost. (To recover the data, the operator must reload the 1442 with the appropriate cards.)

In the CPU, the information needed for execution of the add instruction is taken out of CPU registers and placed in local The UCW (Unit Control Word) that storage. pertains to the 1442 is then taken out of MPX storage and placed in the appropriate CPU registers. The UCW is used to indicate how the byte from the 1442 should be handled (such as where it should be stored in main storage). As soon as the byte is processed and the UCW contents are updated, the UCW is stored into MPX storage. The CPU registers are loaded from local storage with the necessary add instruction information, and the add operation is continued. The next request for service by the 1442 results in repetition of the operations just described.

CPU information is not always restored into CPU registers after a multiplexor channel data byte transfer. If another request for I/O data transfer is made soon enough, then that data is processed. This operation can occur, for example, when a high-speed device (such as a magnetic tape unit) is run on the multiplexor channel.

The maximum number of I/O units that can be attached to the multiplexor channel depends upon:

- The number of available UCW's in MPX storage.

- The number (if any) of shared subchannels used.

- 3. The restriction that a maximum of eight adapters (CU's) can be connected to the standard I/O interface cable.

Item 1 depends upon the model. Up to 32 subchannels (UCW's) can be used in Model

### Selector Channels

- Data transfer for an I/O unit is completed on a <u>record</u> basis before another I/O unit can be started on the same selector channel.

- A selector channel uses its own circuitry (including clock) to effect data transfers between its attached I/O units and main storage.

- Selector channels use CPU circuitry during starting, chaining, and ending procedures. If any overlapping CPU instruction processing is also taking place, the CPU instruction information is stored in local storage until completion of the selector channel operation.

- Up to 256 I/O addresses can be used to address units on a selector channel. The actual number of I/O units will probably be less than the maximum, however, because only eight adapters (I/O control units) can be attached to a standard I/O interface cable.

Either of the two selector channels available for Model 30 operates in burst mode only. Only one device at a time can be actively engaged in a data transfer on a specific selector channel.

Each selector channel has its own circuitry for use in data transfers. When a selector channel data transfer occurs, CPU instruction processing is stopped only for the time necessary to transfer the data byte between main storage and the channel. Because only one device at a time can be operated, a separate area for storage of selector channel UCW's is unnecessary. That is, for each selector channel there is only one current UCW, which is handled by C30; up to 96 in Models D30, E30, and F30 as a standard feature. Models E30 and F30 can have the Additional Multiplexor Subchannels optional feature that provides for use of up to 224 subchannels. In this last case, shared subchannels are not allowed.

A shared subchannel is used for multiple I/O units controlled, one at a time (i.e., no multiplexing between the sharing units), by a single CU. An example of this type of configuration is several direct access mechanisms (such as 2311 disk storage drives) connected to one CU. Only one UCW is used to store controlling information for operation of one of the direct access mechanisms at a time. Use of certain unshared UCW's (i.e., a UCW devoted to only one I/O unit) is excluded if shared subchannel addresses are used. For further information on multiplexor channel addressing, refer to Field Engineering Manual, IBM 2030 I/O Control, System/360, Model 30, Form Y24-3362.

selector channel circuitry. Operation indicated by the current UCW is completed before another I/O operation can be started on the same selector channel. Hence, current CPU instruction information is not stored into local storage (as it is during multiplexor channel data transfers).

During transfer of a byte of data between main storage and a selector channel the CPU clock is not used. Rather, each selector channel has its own clock to control operation of storage. After the data transfer is completed, the CPU clock is used for processing the CPU instruction in progress.

# Introduction

Note that in selector channel starting, chaining, and ending operations, CPU control circuitry is used. For chaining and ending operations, information related to the CPU instruction in progress is placed in local storage.

CPU instruction-processing information is restored into machine registers from local storage at completion of the chaining or ending procedure. Instruction processing is then continued in overlap fashion with any selector channel data transfers

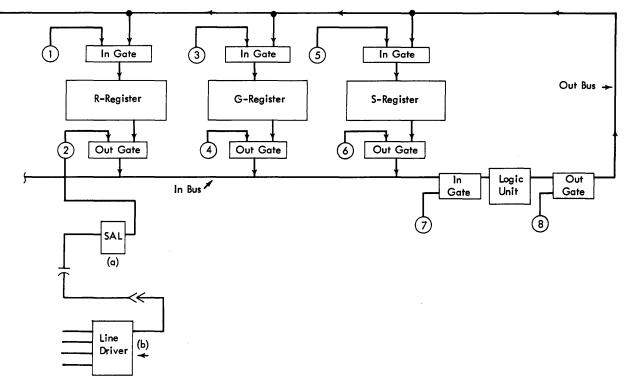

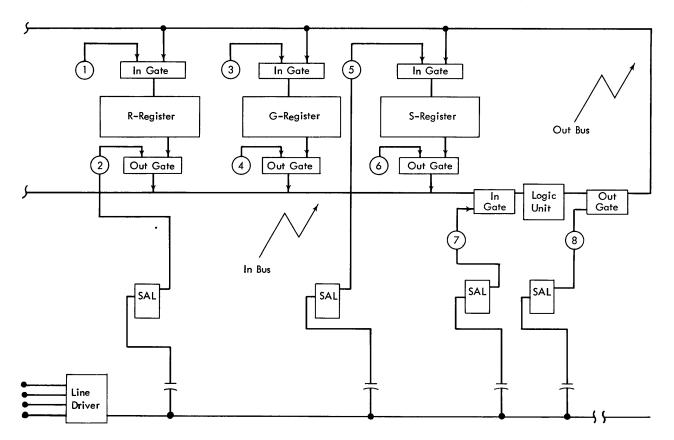

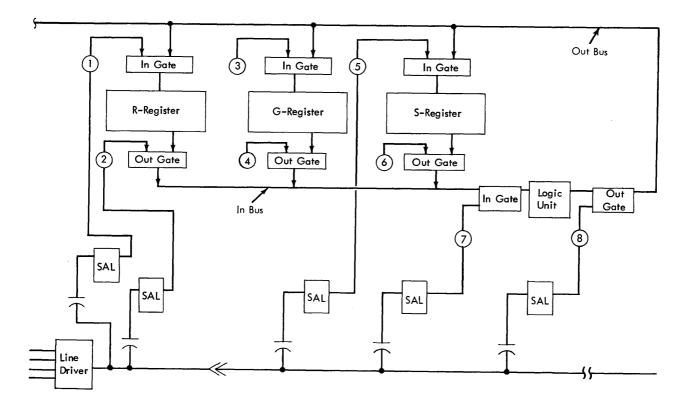

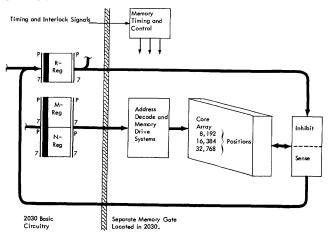

## CPU DATA FLOW

that occur. (Note that during <u>starting</u> of an I/O operation, the CPU instruction in progress is an I/O instruction such as START I/O.)

The eight-bit unit addressing scheme allows for up to 256 separate I/O addresses on a selector channel. However, because only eight CU's (also called adapters) can be attached to a standard I/O interface cable, the actual number of I/O units will probably be less than the maximum addressable number.

- The series of logical steps used to control information flow between machine elements (such as ALU, machine registers, and storage) for a particular operation, is called a ROSmicroprogram routine.

- The ROS microprogram is not written by the user or problem programmer; its routines are established in <u>circuitry</u>, and ROS micro instructions are not stored in core storage.

Recall that ROS (Read-Only-Storage) is the basic control circuitry in the 2030. The particular series of ROS steps taken to control an operation is a microprogram routine. The ROS-microprogram routine for any specific machine operation is, in general, dependent upon:

- The requirements of the operation (i.e., what machine elements must be used to achieve the desired results).

- The logical methods used by the microprogrammer.

It is important to realize that the microprogram is part of the machine circuits and has nothing to do with the writing of problem or control programs. ROS microinstructions are not stored in core storage. A description of ROS is provided in <u>Chapter 2</u> of this publication. The function of a particular machine register, as used in a specific operation, is dependent, to some degree, on how the microprogram for that operation is written. Hence, in this chapter, subsequent introductory descriptions of machine registers and their general functions do not necessarily apply to all operations. Rather, the most usual functions are described.

Many times, reference is made to a bit position in a register. Most registers can hold one byte (eight information bits plus one parity bit) of data. Reference to a bit position within a register is done by prefixing the bit position with the lettername of the register. For example, the high-order bit in the R register is referenced by R0.

#### BUSSES

• Busses are circuits that provide for transfer of information between various machine elements.

Busses provide the information-paths between machine elements such as registers, ALU, and core storage. In many operations, microprogram steps call for transfer of information from a register to a bus and from there to another register. For example, an address byte can be incremented by 1, by:

- Gating the original address byte out of a register to a bus,

- Sending the address byte through ALU while adding 1 to it as it passes through ALU,

- 3. Sending the result byte from ALU to another bus, and

4. Sending the result byte back into the original register.

Most busses in the 2030 handle 8 information bits plus 1 parity bit (one byte).

# MACHINE REGISTERS

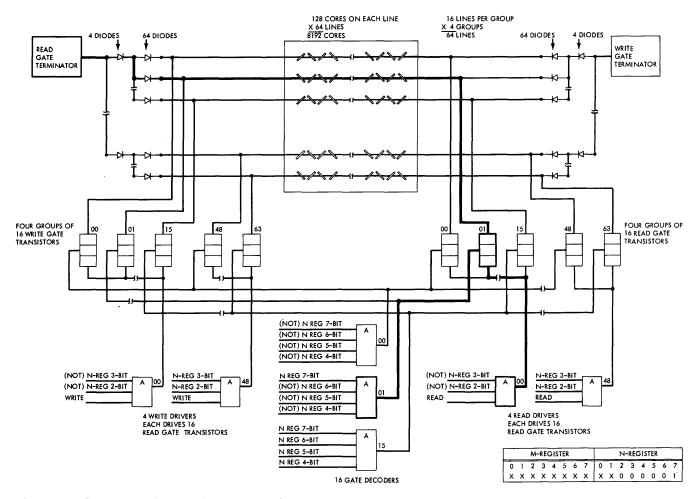

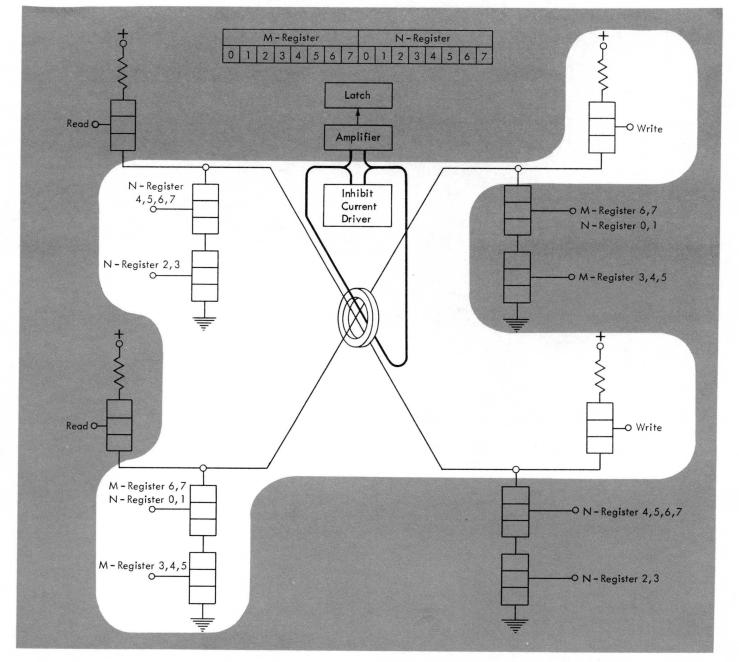

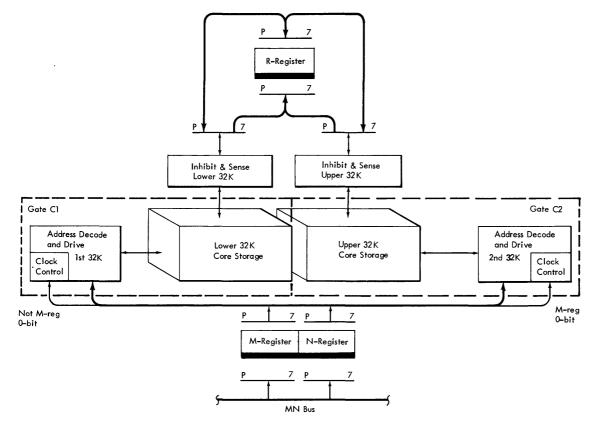

- The M and N registers are set with information used to address core storage locations.

- The R register (storage data register), in general, is:

- 1. The immediate source register for a byte to be stored into a core storage location.

- 2. The immediate destination register for a byte read out of core storage.

- In general:

- 1. Information used to <u>address instructions</u> is sent from the I and J registers to the M and N registers.

- Information used to <u>address data</u> is sent from the U and V registers to the M and N registers.

- 3. Information used to <u>address certain auxiliary storage</u> <u>locations</u> is sent from the T register to the N register.

- The G register usually contains the operation code.

Any position of core storage can be located, for reading or writing purposes, by use of address information placed in the M and N registers. Each of these registers can contain one byte. Hence, a maximum address of 65,535 (decimal) can be represented by the 16 bits in the M and N registers. (That is, the maximum number represented by 16 binary digits is  $2^{16}-1$ .) This arrangement provides for addressing from 0000 to FFFF, or a total of 65,536 (decimal) storage locations.

In the 2030, the M and N registers always have the capacity to hold the bit structure that represents the address FFFF (i.e., for Model 30F). However, any address reference outside of the actual range of main storage positions available (Model 30C has 8192 bytes; Model 30D has 16384 bytes; Model 30E has 32768 bytes) may cause an addressing exception (a program interruption).

Other circuits are used in conjunction with the output of the M and N registers when auxiliary storage (local or one of the MPX storages) is addressed. The actual address is specified in the M and N registers while these other circuits determine to which storage area (main, local, or a MPX) the address applies. The 8 high-order bits of the address are set into the M register, while the 8 low-order bits are set into the N register. The M and N storage address registers are frequently referred to as one register (viz., the MN-register).

Some busses handle less than a byte. The

need for busses of differing capacities will become more evident when you study

detailed machine circuitry.

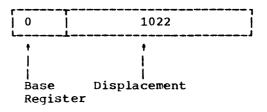

Addressing compatibility is maintained with other System/360 Models because of the base-displacement addressing method used. Recall that addresses are derived from a 12-bit displacement plus a 24-bit base. For example, a program segment that might be written for a System/360, Model I 65 might use storage addresses in the 500,000 to 504,000 (decimal) range. Here, the base register used could have 500,000 as the base address. Displacement values could then run from 0 to 4,000 (decimal). To run this program segment on a Model D30, the base register could be loaded with the address 0 (decimal), and the displacement values left unchanged. Because displacement values cannot exceed FFF (i.e., 12 bit positions are used for displacement) any Model 30 can handle any displacement value in its M and N registers. However, any base-plus-displacement value that exceeds the storage capacity of the System/360 model used may, as previously mentioned, cause an addressing exception.

In general, data written into (or read from) storage passes through the R register. (One notable exception is that when data is transferred between a selector channel and main storage, it does not pass through the R register. Refer to the Field Engineering Manual of Instruction, <u>IBM 2030</u> <u>I/O Control</u>, Form Y24-3362.)

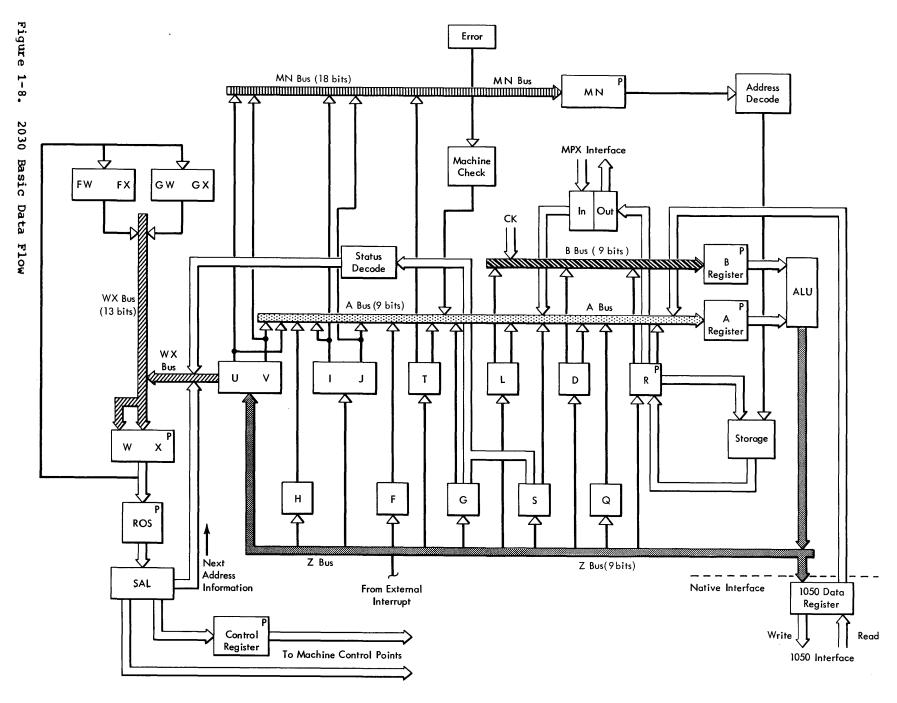

Notice in Figure 1-8 that the MN-bus (really the M and N busses--eight information bits plus one parity bit for each bus) provides input paths to the MN-registers. The following table summarizes the address information source inputs to the MNregisters:

Source Destin- Usual Immediate Register ation Source\_of

- I M High order address bits for an instruction byte

- J N Low order address bits for an instruction byte

- U M High order address bits for a data byte

- V N Low order address bits for a data byte

- T N Address bits for certain auxiliary storage locations

Addresses are frequently obtained from instructions which are in main storage. Hence, there must be a path, during normal instruction processing, over which these addresses can be set into the U, V, I, J, or T registers. One path is from storage, to the R register, through the A-register inputs to ALU, through ALU to the Z bus, and from there to the appropriate register (Figure 1-8). This description is not meant to imply that every time a byte is sent from storage it follows the path just described into all registers. The microprogram specifies which registers are to take part in the operation, and, as already pointed out, the microprogram steps used depend upon the operation being performed.

During instruction processing, the Gregister usually contains the instruction operation code. Hence, the values of the bit positions of this register indicate such items as instruction length and format.

Many other registers are used. However, how a register is used is mainly dependent upon the operation performed. The following table summarizes the usual functions of some important registers in the data flow (Figure 1-8):

## Register Usual Function

- I Instruction address (high-order bits) J Instruction address (low-order

- bits)

- U Data address (high-order bits)

- V Data address (low-order bits)

- L Data length

- T Auxiliary storage address

- D General purpose data register

- R Storage data register

- S Status (CPU)

- G Instruction operation code

- H Priority status register

- Q Storage-Protection key in PSW (High 4 bits); Storage-Protection key of block of storage just used (low 4-bits)

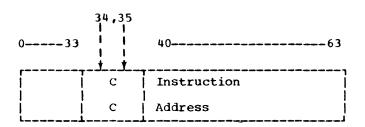

- C Interval Timer Count

- F External Interrupt: Interval Six direct-control interruptions (bits 2 through 7).

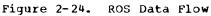

The W and X registers hold information that is used to address ROS. A maximum of 13 bits are needed to address any ROS word. The W register holds the 5 high-order bits and the X register holds the 8 low-order bits. (Note that the W register has only five bit positions which are W3, W4, W5, W6, and W7.) In addition, each of these registers has a parity bit position.

The FW-FX and GW-GX registers are backup registers for ROS addresses. The FW-FX registers are used to retain the ROS address just held by the WX registers when certain multiplexor channel operations break into CPU instruction processing. The GW-GX registers provide backup for addresses in WX when selector channel one requires use of ROS (such as in chaining operations). A similar set of registers (HW-HX) is used during ROS operations for selector channel two. For detailed information about the WX registers, refer to Chapter 2 of this publication. Multiplexor and selector channel operations and register usage) are described in Field Engineering Manual of Instruction, IBM System/360 Model 30, 2030 I/O Control, Form ¥24-3362.

1-12 (9/1/66)

#### ARITHMETIC OPERATIONS

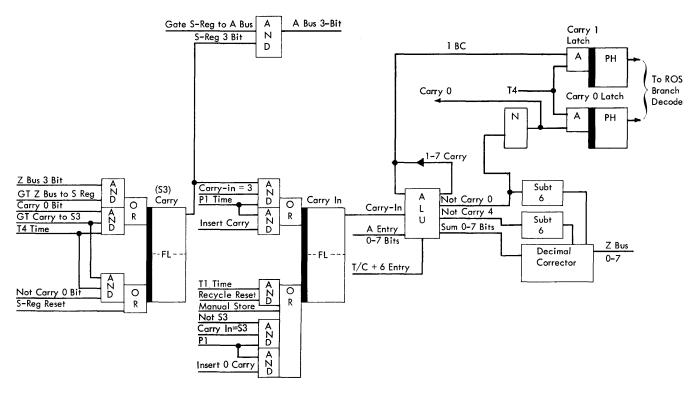

- The B-register input to ALU is complemented in certain arithmetic operations. In some packed decimal operations the B-register input to ALU is incremented by 6.

- Each second operand (source) byte is sent to the B-register during arithmetic operations.

Certain arithmetic operations require complementation of second (source) operand bytes. Some packed decimal operations require addition of 6 to each second operand byte. These two functions are handled by circuits that affect the outputs of the B-register (but not the A-register outputs). Therefore, a source byte is set into the B-register input to ALU and the destination (first operand) byte is set into the A-register input to ALU. In the following descriptions, actual circuit functions (including ROS controls) are not presented. Rather, the general arithmetic procedures used by ALU are presented. If you need to review binary or hexadecimal numbering systems in order to understand the following descriptions of arithmetic operations, refer to the <u>Numbering Systems</u> section in <u>Chapter 1</u> of this publication.

### FIXED POINT ARITHMETIC

- In fixed-point numeric operands, all bit positions to the left of the high-order significant digit have the same value as the sign bit.

- The maximum positive number that can be contained in a binary field of n digits is equal to  $2^{n}-1$ .

- The maximum negative number (in two's-complement form) that can be contained in a binary field of n digits is equal to 2<sup>N</sup>.

Recall that fixed-point binary operands are stored as half words or words with the sign indicated in the high-order bit position. When the high-order position has a value of 0, the binary number is positive. A negative number has a sign bit at a value of 1. The remainder of the halfword or word is used to designate the magnitude of the number. However, all bit positions between the leftmost significant digit and the sign bit have the same value as the sign bit. For example, either of the following are positive numbers:

+S 0 000 0000 0000 1000 +S 0 111 1111 1111 1000

But, both of the following are negative numbers:

-S 1 000 0000 0000 0000 -S 1 111 1111 1111 1011 When all of a given number of binary digits are 1, the largest positive quantity that can be represented by that number of digits is given. For example, the maximum positive number represented by two binary digits is 11 (decimal 3). The maximum positive quantity represented by a binary field can be expressed in decimal notation by:

- Counting the number of binary digit positions in the field.

- 2. Raising 2 to a power equal to the count determined in step 1.

- 3. Subtracting 1 from the product obtained in step 2.

Hence, the maximum positive quantity represented by four binary bits is 2\*-1 (15 in decimal).

Because one of the sixteen bit positions in a fixed-point half word is used for the sign, fifteen bit positions can be used for the integer. Therefore, the maximum positive quantity that can be represented in a fixed-point binary half word is  $2^{15}-1$  (32,767 in decimal).

In fixed point operations, negative numbers are carried in two's-complement form. For example, the true binary form of the decimal value +26 is changed to a negative quantity by complementing it:

| Decimal Value | Sig | n   |      |      |            |

|---------------|-----|-----|------|------|------------|

| +26           | 0   | 000 | 0000 | 0001 | 1010       |

|               | 1   | 111 | 1111 | 1110 | 0101<br>+1 |

| - 26          | 1   | 111 | 1111 | 1110 | 0110       |

Notice that the two's-complement of 11010 (+26) is 00110. The remainder of the bit positions are at a value of 1 to indicate a negative quantity.

The maximum negative number that can be represented in a half word is:

~

1 000 0000 0000 0000

This is the complement of 1 0000000 0000 0000 which should represent a positive quantity. However, the convention is that the high-order bit of a half word is 0 when the quantity is positive. To show 1 0000000 0000 0000 as positive would require an extra high-order position at a 0 value. But this is impossible because only 16 positions are provided in a half word. Hence, in a half word, the absolute value of the largest negative number is one greater than the absolute value of the largest positive number. This concept also applies to quantities represented in a word. A summary of the magnitude of binary numbers that can be represented in a word is shown in Figure 1-9.

| Number  |       | Decimal     | S   |         | Integ    | ger      |          |

|---------|-------|-------------|-----|---------|----------|----------|----------|

| 231 - 1 | = 2   | 147 483 647 | =0  | 111111  | 1111111  |          | 1111111  |

| 216     | =     | 65 536      | =0  | 0000000 | 00000001 | 00000000 | 00000000 |

| 20      | =     | 1           | =0  | 0000000 | 00000000 | 00000000 | 0000000  |

| 0       | =     | 0           | =0  | 0000000 | 00000000 | 00000000 | 0000000  |

| -20     | ,=    | - 1         | =1  | 111111  | 11111111 | 1111111  | nnm      |

| -21     | =     | -2          | =1  | 1111111 | 11111111 | 11111111 | 1111110  |

| -216    | Ξ     | -65 536     | = } | 1111111 | 11111111 | 00000000 | 0000000  |

|         | =-2   | 147 483 647 | =1  | 0000000 | 00000000 | 00000000 | 0000000  |

| -231    | = - 2 | 147 483 648 | =1  | 0000000 | 00000000 | 00000000 | 0000000  |

Figure 1-9. Fixed Point Numbers

## Fixed Point Addition

• An overflow is indicated when the carry-conditions, out of the high order digit position and out of the sign position, do not agree.

An overflow occurs when two numbers are arithmetically manipulated into an area, such as a half word, that is not large enough to contain the result. In fixedpoint operations, an overflow condition is indicated when the carry out of the highorder digit position and the carry-out of the sign position do not agree.

The following addition examples illustrate fixed point binary addition. Only eight bit positions are used; the high-order bit is the sign. Carry conditions and any consequent overflow results are summarized for each example:

- a. No carry out of high order digit position.

- b. No carry out of sign position.

- c. Carries agree; therefore, no overflow.

S 2. +57 = 00111001

-35 = 11011101

- +22 = 00010110 (true form)

- a. Carry out of high order digit position.

- b. Carry out of sign position.

- c. Carries agree; therefore, no overflow.

S 5. -57 = 11000111S  $\frac{-92}{-149} = \frac{10100100}{01101011}$ 3. +35 = 00100011-57 = 11000111-22 = 11101010 (complement form) a. No carry out of high order digit a. No carry out of high order digit position. position. b. No carry out of sign position. b. Carry out of sign position. c. Carries agree; therefore, no overc. Carries do not agree; therefore, flow. overflow. S S 4. -57 = 110001116. +57 = 00111001 $\frac{-35}{-92} = \frac{11011101}{1010000}$  (complement form) +92 = 01011100+149 = 10010101a. Carry out of high order digit posia. Carry out of high order digit position. tion. b. Carry out of sign position. b. No carry out of sign position. c. Carries do not agree; therefore, c. Carries agree; therefore, no overoverflow. flow.

## Fixed Point Subtraction

- The two's-complement of the second operand is added to the first operand in fixed-point subtract operations.

- An overflow occurs when the carry conditions out of the high-order digit position and out of the sign position do not agree.

Fixed-point subtraction is done by adding the two's-complement of the second operand to the first operand.

An example is subtraction of +456 from +678. +456, the second operand, is complemented and added to +678, the first operand.

$\begin{array}{rrrr} +678 & 001010100110 \text{ (first operand)} \\ (-) & +456 & \underline{111000111000} \text{ (2nd operand comp.)} \\ +222 & 000011011110 \end{array}$

Overflow occurs when the carry out of the high order digit position does not agree with the carry out of the sign position. For example:

- $(-) \begin{array}{c} 32,766 & 1 & 000 & 0000 & 0001 \\ + & 20 & 1 & 111 & 1111 & 1110 \\ -32,786 & 0 & 111 & 1111 & 1110 & 1101 \end{array} (Comp)$

- a. No carry out of high order digit position.

- b. Carry out of sign position.

c. Carries do not agree; therefore, overflow.

In any fixed-point binary subtract operation, each second operand byte, as it is operated on by ALU, is effectively complemented. Recall that data is sent through ALU in complemented and true form. In the binary subtract operation, the complement lines of the second operand byte are added to the true lines of the first operand byte. The complement lines are really the one's-complement of the second operand byte. To obtain the correct result, a one is forced (by control circuitry) into the low-order bit position (bit7) of ALU when the low-order bytes are added. In this process, then, the inversion plus the one in the low-order position effectively results in addition of the two's-complement of the second operand byte to the first operand byte. For example:

- 1. Operation: fixed-point binary subtract.

- 2. First operand: 00000001

- 3. Second operand: 11111111

4. Operation on high order bytes: Action in ALU: 4. First operand in true form = 0 000 0001 1st operand byte = 0000 0001 Second operand inverted = 0 000 0000 2nd oper. byte inverted =0000 0000 No forced carry. Forced carry = 0 000 0010 Result =Result high-order byte = 0000 0001 The forced carry is automatic only for the low order byte addition. Consider, for Resulting half word: 5. example, subtraction of -1 from +496. (Half word operands are used.)  $0\ 000\ 0001\ 1111\ 0001\ =\ +497$  (decimal) 1. First operand = 0 000 0001 1111 0000 2. Second operand = 1 111 1111 1111 1111 6. Equivalent operation in decimal notation: +496 - (-1) = +4973. Operation on low order bytes: If a carry occurs out of the high order bit First operand in true form = 1111 0000 position of a result byte, then that carry Second operand inverted = 0000 0000 is added to the low order position of the next two-byte addition. Forced carry = Result low-order byte = 1111 0001

# PACKED DECIMAL ARITHMETIC

- In packed decimal add or subtract:

- 1. An even number of minus signs indicates a true add.

- 2. An odd number of minus signs indicates a complement add.

Recall that the sign of a packed decimal field is in the four low-order bits of the low-order byte. Sign analysis must be made before any adding or subtracting is started. The result of the sign analysis indicates whether or not the second operand byte syst bitAn even number of minus signs specifies a true-add operation, while an odd number of minus signs specifies a complement-add operation. The eight possible combinations are:

| bytes are to be complemented. When the<br>system is using the EBCDI code, the sign<br>bit-combinations are: | <u>Operation</u> | Sign of<br>First<br><u>Operand</u> | Sign of<br>Second<br><u>Operand</u> | True or<br>Complement_Add |

|-------------------------------------------------------------------------------------------------------------|------------------|------------------------------------|-------------------------------------|---------------------------|

| Dit Combination Give Depresented                                                                            | add (+)          | +                                  | +                                   | true                      |

| Bit Combination Sign Represented                                                                            | add (+)          | -                                  | +                                   | complement                |

| 1100 +<br>1111 +                                                                                            | add (+)          | -                                  | -                                   | true                      |

| 1101 -                                                                                                      | add (+)          | +                                  | -                                   | complement                |

| Three conditions are analyzed to deter-<br>mine how the operation is to proceed:                            | subtract (-      | -) +                               | •                                   | complement                |

| 1. The operation: add (+) or subtract (-)                                                                   | subtract (-      | -) -                               | +                                   | true                      |

| 2. The sign of the first operand: + or -                                                                    | subtract (-      | -) -                               | -                                   | complement                |

| 3. The sign of the second operand: + or -                                                                   | subtract (-      | -) +                               | -                                   | true                      |

#### Packed Decimal True Addition

• Decimal corrector circuits are used to prevent a four bit binary sum from representing a hexadecimal digit rather than the desired decimal digit.

Values of four binary bits in the range 0000 to 1001 can represent decimal digits in the range 0 to 9. Addition of two fourbit binary numbers results in a total that represents a decimal digit as long as the total does not exceed 9. If the total exceeds 9, then the result is outside the range of single decimal symbols representable by the four binary bits. For example:

0001 + 1000 = 1001

$$(1 + 8 = 9).$$

But:

0010 + 1000 = 1010

(2 + 8 = 10)

In the last addition, the resulting four binary bits represent two decimal digits. Four bits in packed decimal fields, however, <u>must</u> represent only the single decimal digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, or 9. Decimal corrector circuits are used to prevent two four-bit groups from giving a result outside of the range of a single decimal symbol.

After sign analysis, packed-decimal true add proceeds as follows:

- Six (0110 in binary) is added to each four bit digit group of the second operand byte.

- The entire first operand byte (or only four high-order bits for low order byte) is added to the step 1 sum. Any carry out of a four-bit total is noted.

- If, in step 2, a carry occurred out of the high-order bit of a four-bit sum, add 0000 to that sum. If such a carry did not occur, add the complement of 0110 (i.e., 1010) to that sum.

For example, ignoring sign analysis, add+18 (first operand) to +16 (second operand):

Add 6 (0110) to each four bit group of the second operand:

| Second | operand | (16) | = | 0001        | 0110 |

|--------|---------|------|---|-------------|------|

|        |         |      |   | <u>0110</u> | 0110 |

|        |         |      |   | 0111        | 1100 |

It is of some interest to note that this addition has resulted in conversion from ten's complement notation. That is, 1 (0001) is the ten's complement-of-9 (1001). Addition of 6 (0110) to the ten's complement-of-9 produces the sixteen's complement-of-9 which is 7 (0111). Also, 6 (0110) added to the ten's complement-of-4 (which is 6 or 0110) produces the sixteen's complement-of-4 (which is 12 or 1100).

Add the first operand byte to the sum obtained in step 1. (Any carry out of the high bit position of the four low bits is carried into the low order bit of the four high bits.)

| Sum from step | 1 =  |   | 0111 | 1100 |

|---------------|------|---|------|------|

| First operand | (18) | = | 0001 | 1000 |

| -             |      |   | 1001 | 0100 |

If this addition results in a carry out of a four-bit group, then the maximum hexadecimal digit (F) has been exceeded. But the first ten hexadecimal symbols (0 through 9) equate directly to the corresponding decimal symbols. Therefore, if a carry-out does occur, the digit represented by that four-bit group must be in the range 0000 to 1001 (0 to 9). On the other hand, if no carry-out occurs, then the four-bit group does not represent the desired decimal digit, and the 6 originally added into that group must now be subtracted.

Add 0000 to a four bit group if a carry out of its high order position occurred. Add 1010 (complement of 6) to a four bit group if a carry did <u>not</u> occur out of its high order position.

| 1001 | 0100 |    |            |

|------|------|----|------------|

| 1010 | 0000 |    |            |

| 0011 | 0100 | or | +16+18=+34 |

(Note that the carry out of the high order position is not used as part of the total.) As a second example, consider addition of two packed decimal fields:

- 1. Second operand

(138+): 0001 0011 1000 1100

First operand

(117+): 0001 0001 0111 1100

- The low order bytes are sent to ALU. A true add is indicated because the number (zero) of minus signs is even.

- 3. The four high order bits of each low order byte are added:

- a. First, six is added to the second operand:

- 1000 +<u>0110</u> 1110

- b. Then the first operand is added to the sum obtained in step 3a:

- $1110 + 0111 \\ 0101$

The carry is retained for use in addition of the next two four bit groups.

- c. Because a carry occurred out of the high order position, 0000 is added to the result of step 3b:

- 0101 + $\frac{0000}{0101}$  + = (5 decimal)

- 0101 represents the result low

## First Operand Second Operand

Before operation 0001 0011 1000 1100 0001 0001 0111 1100 After operation 0010 0101 0101 1100 0001 0001 0111 1100

(In decimal notation: + 138 + 117 = +255.)

order decimal digit. 0101 and the sign 1100 are stored in the low order byte position of the destination field (first operand location).

- 4. The next two bytes (one from the first operand, one from the second operand) are sent to ALU.

- 5. The two bytes are added:

- a. Six is added to each four bit group of the second operand byte:

- $\begin{array}{c} 0001 & 0011 \\ + \underline{0110} & + \underline{0110} \\ 0111 & 1001 \end{array}$

- b. The first operand and the carry from step 3b are added to the sum obtained in step 5a:

- Carry from step 3b =1Sum from step 5a =0111First operand = $\frac{0001}{1000}$  $\frac{0001}{1011}$

- c. Because a carry did not occur out of either four bit group, 1010 is added to each group:

- 1000 1011 1010 1010

- 0010 0101

Notice that the high bit carries of each four bit group are not used in the total. The result is placed in the first operand location. Summarizing this operation:

### Packed Decimal Complement Addition

• In complement add, the complement value of the second operand byte is added to the true value of the first operand byte.

Packed decimal complement addition employs decimal correction circuits in a different way than true add. After sign analysis, packed decimal complement add proceeds as follows:

- 1. The portion of the second operand being operated on is complemented.

- 2. The portion of the first operand being operated on is added to the result of step 1. Carry conditions out of each participating four-bit group are noted.

- If, in step 2, a carry occurred out of a four-bit group, add 0000 to that group; if no carry occurred, add 1010 (the complement of 0110) to that group.

- 4. If there was a carry out of the highorder four bits in step 2, the answer is in true form. If there was no carry out of the high-order four bits in step 2, the answer is in complement form and must be recomplemented. In this case, take the 2's complement of the number and decimal correct those four-bit groups where no carry occurred. The procedure is:

- a. Invert each position of the complement answer and add 1 to the low-order position.

- b. Decimal correct by adding 0000 to each four-bit group that has a carry out, and 1010 (2's complement of 6) to each four-bit group that has no carry out.

For example, subtract 15 (second operand) from 18 (first operand):

1. Complement the second operand.

Second operand (16) = 0001 0110

(complemented) = 1110 1010

2. Add first operand to result of step 1.

Result of step 1 = 1110 1010 First operand (18) =  $\frac{0001 \ 1000}{0000 \ 0010}$  3. Carries occurred out of each four bit group. Therefore, add 0000 to each group. The result is in true form.

| 0000 | 0010 |

|------|------|

| 0000 | 0000 |

| 0000 | 0010 |

In decimal:

18 - (+16) = 2

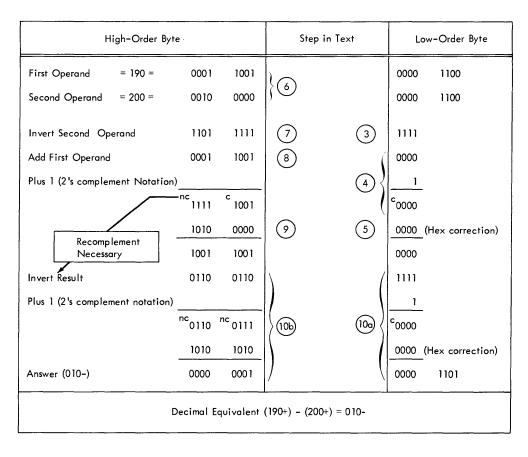

As a second example (summarized in Figure 1-10), consider subtraction of +200 from +190:

1. First operand = 0001 1001 0000 1100

Second operand = 0010 0000 0000 1100

- The low order bytes are sent to ALU. A complement add is indicated because the number of minus signs is odd (one minus for the subtract operation, each operand is plus).

- 3. Invert the four high order bits of the low order second operand byte:

0000 (inverted) = 1111

4. Add the four high order bits of the first operand byte to the result of step 3. Because this is the units position, add 1 to make the notation 2's complement.

Result step 3 = 1111 First Operand = 0000 $\frac{1}{0000}$

- 5. Because a carry did occur from the four-bit group, no decimal correction is necessary.

- The next two bytes (one from each field) are sent to ALU.

# Figure 1-10. Packed Decimal Complement Add Example

# 7. Invert the second operand byte.

8. The first operand byte is added to the inverted second operand. (Note that a carry out of the high-bit position in the first addition--step 4--did not occur. Therefore, no additional carry is used to form this step 8 total.)

| Step 7 result |      | # | 1101 | 1111 |

|---------------|------|---|------|------|

| First operand | byte | Ξ | 0001 | 1001 |

| Result        | -    | = | 1111 | 1000 |

9. A carry did not occur out of the highorder four bit group. Therefore, add 1010 to that group. A carry did occur from the low-order four-bit group. Add zero to this group.

| 1111        | 1001 |

|-------------|------|

| <u>1010</u> | 0000 |

| 1001        | 1001 |

10. There was no carry out of the high order bit of the step 8 result. Therefore, the answer is in complement form and must be recomplemented to produce a true result. a. Read out the low-order byte resulting from step 5. Invert the highorder four bits and add 1 to produce the correct 2's complement notation. High-order four bits = 0000 Inverted = 1111 Plus 1 (2's Comp) = 1 Low-order byte answer = 0000

There is a carry from this four bit group so hexadecimal correction is not needed. Therefore, add 0000 to produce the low-order digit of the answer.

b. Read out the high-order byte. Invert the bits and add the carry from the low-order byte (step 10a). High-Order byte = 1001 1001 Inverted = 0110 0110 Low-order byte carry =  $\frac{1}{0110} \frac{1}{0111}$

> There was no carry from either four-bit group. Therefore, both groups must be hexadecimal-corrected by adding 1010 to each group.

1-20 (9/1/66)

| Result from above =    | 0110 | 0111 |

|------------------------|------|------|

| Hex-correction =       | 1010 | 1010 |

| High-order byte answer | 0000 | 0001 |

11. The result of the addition is stored in the first operand location.

# Floating Point Arithmetic

- Floating point operands are made up of three fields:

- a. fraction sign-bit

- b. characteristic (represents -64 to +63)

- c. fraction (made up of hexadecimal digits)

- Short precision operands are a word in length.

- Long precision operands are a double word in length.

- A normalized fraction has a high order non-zero hexadecimal digit; an unnormalized fraction has a high-order hexadecimal digit of zero.

Floating point is not a numbering system. Rather, it is a way of representing a quantity in any numbering system. This representation takes the form of a series of digits multiplied by the base (of the numbering system used) which is raised to a power. For example, in the decimal system, the number 1,234 is equal to any one of the following:

| 123.4  | Х | 101 |

|--------|---|-----|

| 12.34  | Х | 102 |

| 1.234  | Х | 103 |

| .1234  | Х | 104 |

| .01234 | Х | 105 |

Notice that the decimal point is located at a different position in each of the preceding numbers. It is in fact a <u>floating</u> decimal <u>point</u>.

The significant digit portion of a floating point number is called the fraction, and the power to which the base is raised is called the characteristic. For example, in .1235 x 10<sup>4</sup>, .1235 is the fraction and 4 is the characteristic. Notice that the fraction can be either positive or negative and the characteristic can be either positive or negative:

| .1235 | Х | 104  |

|-------|---|------|

| 1235  | Х | 104  |

| .1235 | Х | 10-4 |

| 1235  | Х | 10-4 |

Very large and very small quantities can be conveniently represented in floating point format. For example:  $.12 \times 10^{20} = 12,000,000,000,000,000,000$

Result =  $0000 \ 0001 \ 0000 \ 1101$

1

0

Decimal Equiv. = 0

$.567 \times 10^{-20} = .000000000000000000567$

Quantities of such magnitudes are frequently used in scientific computations. Hence, floating point (a special feature) is mainly applicable to processing of scientific problems.

In System/360 floating point operands are fixed in length:

- 1. Short precision operands are a word in length.

- Long precision operands are a double word in length.

Floating point operands represent hexadecimal numbers. The areas in a floating point word and double word are:

|                      | Word                 |

|----------------------|----------------------|

| S Characteristic     | Fraction             |

| 0 1                  | 7 8 31               |

|                      | Double Word          |

| S Characteristic     | Fraction             |

| 0 1 7                | 8 63                 |

| The sign bit positic | n is at a value of 0 |

for positive <u>fractions</u> and at a value of 1 for negative <u>fractions</u> and at a value of 1

| Hexadecimal Fraction | <u>Sign Bit Value</u> |

|----------------------|-----------------------|

| +.12                 | 0                     |

| 12                   | 1                     |

Up to 6 hexadecimal digits can be represented by the 24 bits of the fraction field in a word. (During addition, subtraction, and division operations, however, a seventh digit-the guard digit-is used to increase the precision of the result.) A double word fraction can contain up to 14 hexadecimal digits. (A guard digit is not used here.)

The hexadecimal point of the fraction is assumed to be immediately to the left of the high-order fraction digit.

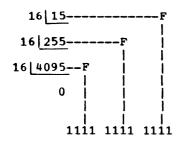

The sign of the fraction is taken care of by the sign bit, but notice that there is no sign bit for the characteristic. The characteristic portion in a word or double word is seven bits long. The maximum magnitude of a positive number represented by 7 binary bits is 27 -1 or 127; the smallest magnitude is 0. In order to represent positive and negative exponents, the value 1000000 (64 in decimal), of the seven bits that comprise the characteristic, is recognized by the system as a characteristic of 0. The maximum positive characteristic is then 1111111 and the maximum negative characteristic is 0000000. Hence, the characteristic is negative if the bit structure of the characteristic field is in the range 0000000 to 0111111 (0 to 63 decimal). This provides a range of negative characteristics from -1 to -64. In other words a characteristic field of 0000011 is recognized by the system as a characteristic of -61. This convention of using 1000000 as zero is called excess 64 notation.

If the characteristic is negative (i.e., a characteristic field in which the high-

order bit is zero), its value can be determined by subtracting it (by complement addition) from 1000000 (64 decimal). For example, if the characteristic field is 0010111:

| Inverted | char. | = | 1101000 |

|----------|-------|---|---------|

| plus 1   |       | = | 1       |

| -        |       |   | 1101001 |

2. Add complement to 1000000:

| 1000000 |

|---------|

| 1101001 |

| 0101001 |

The carry indicates that the answer is in true form, but it is ignored in the result. Therefore: 0101001 = 41 (decimal). Hence, the characteristic represented by 0010111 is -41 (decimal).

To determine the decimal value of a <u>posi-</u> <u>tive characteristic</u>:

- Note that the high order bit must be at a value of 1 for positive characteristics.

- 2. Convert the remaining bit positions to the appropriate decimal value.

For example, 1001001 is a positive characteristic because the high-order digit is 1. The remainder of the characteristic (1001) is equal to 9 in decimal notation. Hence, 1001001 represents a characteristic of +9.

A normalized floating-point number has a non-zero high-order hexadecimal fraction digit. For example, the hexadecimal number +.1A3 x 16<sup>2</sup> in a normalized word (floating point format) is:

| Sign | Characteristic |      |      | Frac | tion |      |      |

|------|----------------|------|------|------|------|------|------|

| 0    | 1000010        | 0001 | 1010 | 0011 | 0000 | 0000 | 0000 |

| +    | +2             | 1    | A    | 3    | 0    | 0    | 0    |

Notice that the three high-order binary fraction digits are 0, but that the high order hexadecimal fraction digit is 1. The fraction is normalized, however, because it is normalized with respect to hexadecimal digits and not with respect to binary digits. An example of an unnormalized fraction is:

|   | 1000011 | 0000 | 1111 | 1111 | 0000 | 0000 | • |  |

|---|---------|------|------|------|------|------|---|--|

| + | +3      | 0    |      | F    |      | 0    | 1 |  |

Normalization is done by left-shifting the fraction digits until the high order hexadecimal digit is non-zero. For each left shift, the characteristic is decreased by one. When normalization is done prior to an arithmetic operation, it is called prenormalization. Postnormalization is a process that changes an intermediate arithmetic result to its normalized form.

## Floating-Point Addition

• The operand fraction with smallest characteristic is rightshifted until the two operands have equal characteristics; then the operands are added.

Before addition starts, the characteristics of both operands are compared. The fraction with the smaller characteristic is right-shifted. For each right-shift, the characteristic is increased by one. When the characteristics of the two operands are equal, shifting stops. The fractions are then added algebraically to form an intermediate sum. If a carry occurs out of the high-order hexadecimal sum digit, the sum fraction is shifted right once and its characteristic is increased by one. If a characteristic overflow occurs as a result of this increase, an exponent-overflow exception (program interruption) occurs.

There are two floating-point add instructions: add normalized and add unnormalized. When the add unnormalized instruction is executed, the sum is stored without normalization. In the normalized add instruction, however, the intermediate sum is left-shifted until the high-order hexadecimal digit is non-zero. For each left-shift of the hexadecimal digits, the characteristic is decreased by one.

For example, add .124 X 16<sup>2</sup> to .0127 X 16<sup>3</sup> using the add unnormalized instruction (short precision assumed):

- 1. .124 X 16<sup>2</sup> is right-shifted once before

the addition starts.

.124 X 16<sup>2</sup> (right-shifted once) = .0124

X 16<sup>3</sup>

- 2. The fractions are added:

| .0127  |  |

|--------|--|

| +.0124 |  |

| .025B  |  |

3. The result is not normalized but it is stored as is:

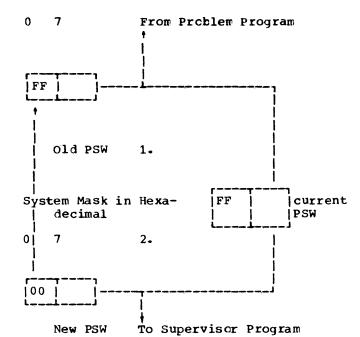

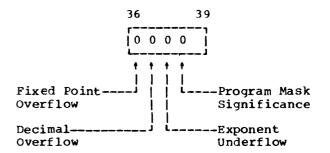

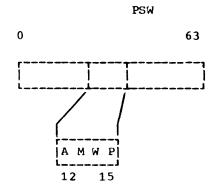

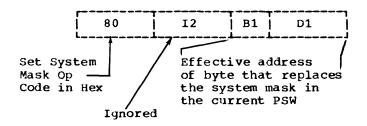

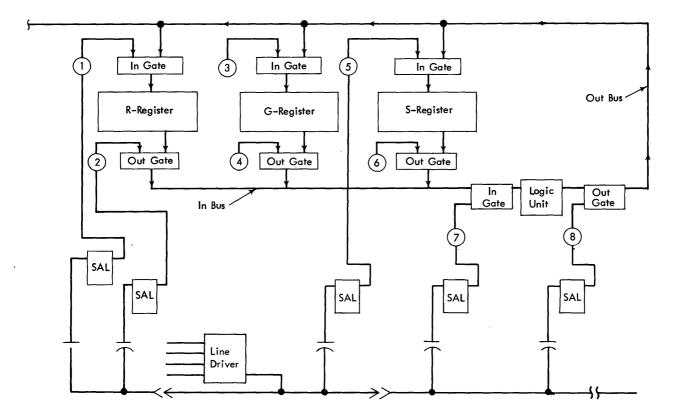

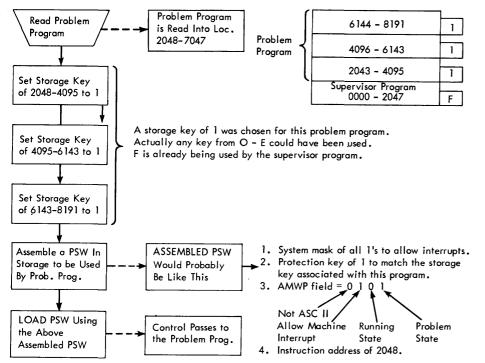

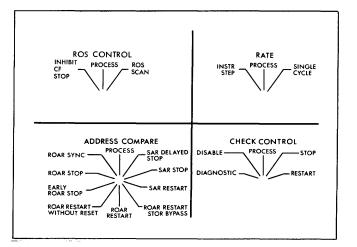

| Sign | Characteristic |      |      | Fract | tion |      |      |