## IBM System/360 Model 30 Operating Guide

This reference publication describes operator procedures for the IBM 2030 Processing Unit and the IBM 1052 Printer Keyboard (attached to the IBM System/360 Model 30). For additional information for operation of the various input/output devices, refer to the publications listed in the <u>IBM System/360</u> <u>Bibliography</u>, Form A22-6822.

#### Third Edition

This is a reprint of A24-3373-1 incorporating changes released in the following Technical Newsletter.

| Form Number | Pages Affected | Date         |      |

|-------------|----------------|--------------|------|

| N24-0390    | 20             | December 28, | 1966 |

Significant changes or additions to the specifications contained in this publication will be reported in subsequent revisions or Technical Newsletters

Copies of this and other IBM publications can be obtained through IBM Branch Offices. This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. 171, P.O. Box 6, Endicott, New York 13760 Address comments regarding this publication to this address.

C International Business Machines Corporation 1965

| IBM SYSTEM/360 MODEL 30 OPERATING       |

|-----------------------------------------|

| GUIDE 5                                 |

| IBM 2030 System Control Panel           |

| Operator's Control Panel (OCP) 6        |

| Console Controls 9                      |

| Operation Controls                      |

| Push Buttons                            |

| Displays                                |

| Use Meters                              |

| SYSTEM OPERATIONS                       |

| System Power-On and Power-Off 19        |

| Program Load Routine                    |

| Display Information From Storage 20     |

| Store Information into Storage 20       |

| Single-Instruction Processing24         |

| Single-Cycle, Display, and Store        |

| Operations                              |

| Processing a Program Section            |

| Starting at a Specific Instruction (Set |

| IC) Procedure                           |

| Manual Intervention                     |

| Microprogram Test Routines              |

| Basic Test                              |

| Display Read/Write Storage              |

| Alter Read/Write Storage                |

| Alter a Block of Read/Write Storage 28  |

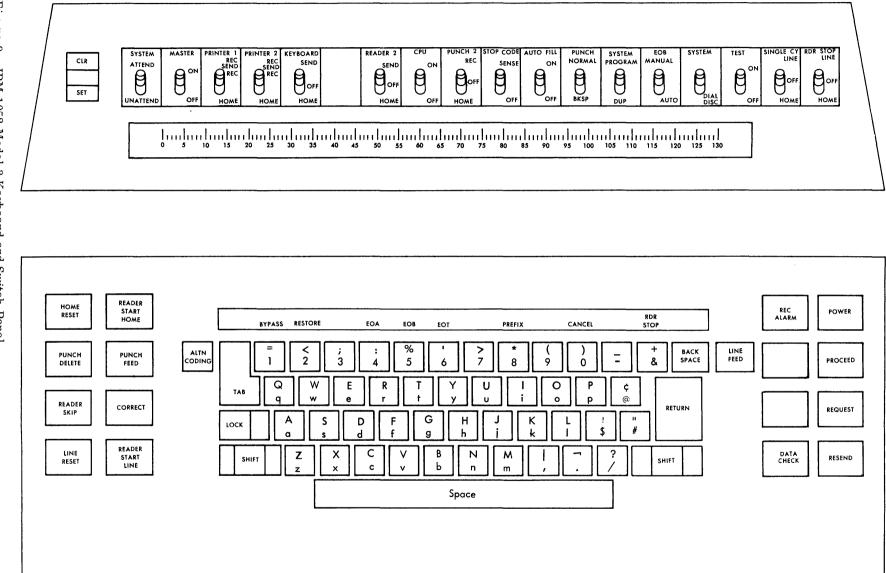

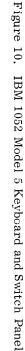

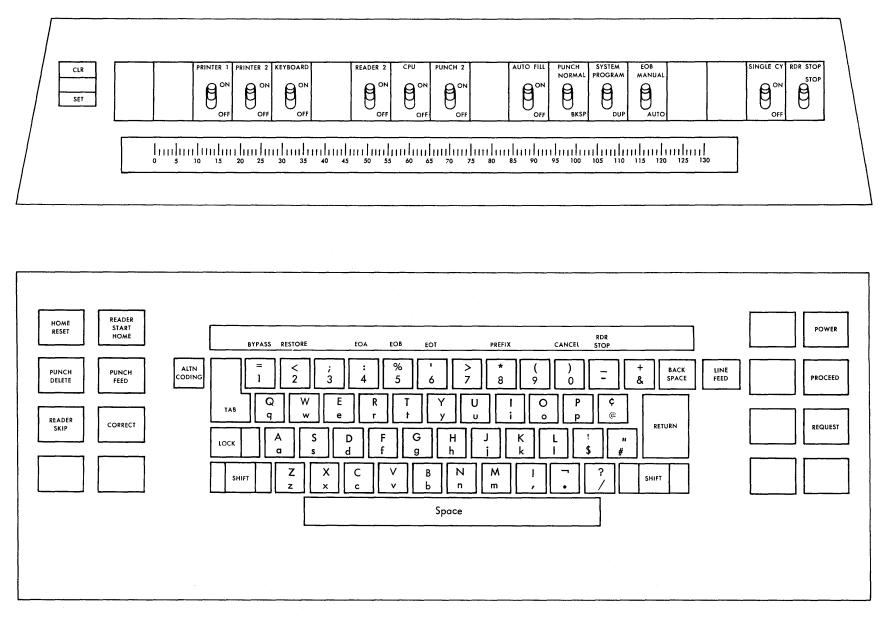

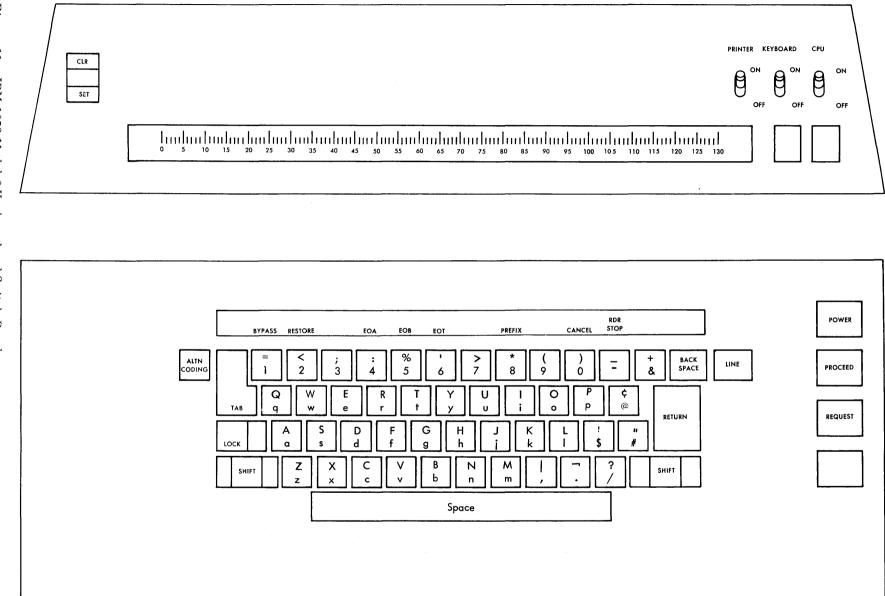

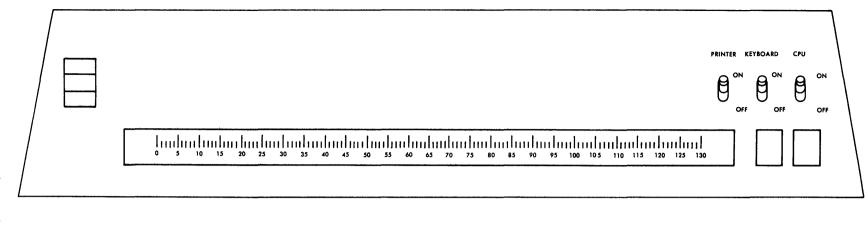

| IBM 1052 PRINTER-KEYBOARD 29            |

| IBM 1050 OPERATIONS                     |

| EXTENDED BINARY-CODED-DECIMAL           |

| INTERCHANGE CODE (EBCDIC)41             |

| GLOSSARY OF TERMS 44                    |

| INDEX                                   |

.

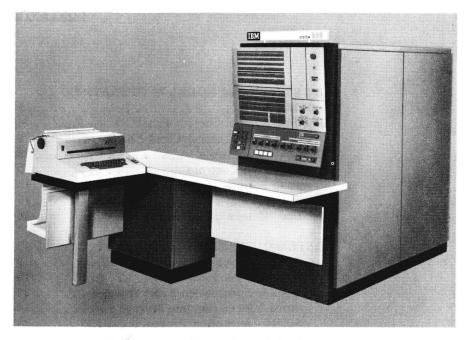

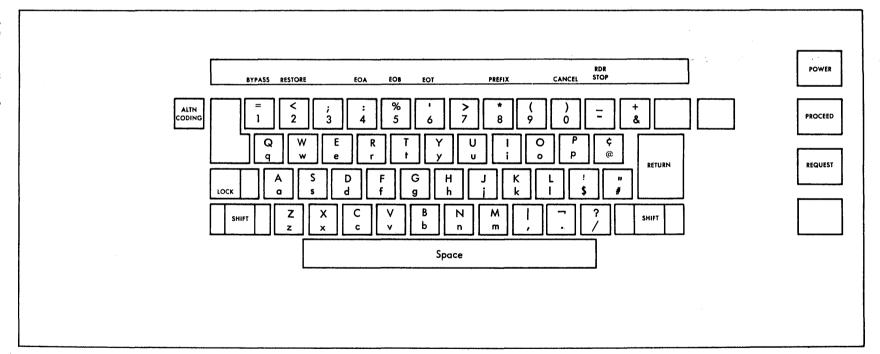

Figure 1. IBM System/360 Model 30 with IBM 1052 Printer Keyboard

The IBM System/360 Model 30 (Figure 1) is a solidstate, high-speed data processing system that is compatible with the other models of System/360 as described in IBM System/360, Principles of Operation, Form A22-6821.

The operator controls needed for normal program processing (turning power on and off and loading and starting a program) are contained on the 2030 system control panel (console). The IBM 1052 Printer-Keyboard can be added to the system so that communication between the operator and the system can be documented. The IBM 2030 Central Processing Unit is provided with a number of indicators and manual controls that permit operation of the system in any of several modes, and observation of the results of any operation. These indicators and controls are assembled on a panel (Figure 2) that serves as both an operator's system control console and an IBM Customer Engineer's panel. The lower right-hand portion of the console is designated as the Operator's Control Panel (OCP). This section contains four push buttons. three 16-position rotary switches, and six indicators. Except for the nomenclature printed on the panel. the OCP is identical on all CPU's (Central Processing Units) in System/360. The OCP contains all controls and indicators necessary for normal problem-program processing.

#### OPERATOR'S CONTROL PANEL (OCP)

This section of the 2030 console (lower right corner) has the following controls and indicators:

#### Power-On Key

The power-on sequence for the CPU and all on-line I/O units starts when this key is pressed. A system reset function occurs. All data-flow registers (but not the general-purpose or floating-point registers) are reset. as are any priorities that happen to turn on. The CPU clock is reset to prevent access to storage so that information in storage is not disturbed. Hence, system power can be turned off and restored without destroying information in main storage.

The I/O units are sequenced ON one by one. If power cannot be brought up for a unit, further power-on sequencing is interrupted (console Power On light remains off) until corrective action is taken for that unit. All on-line I/O units are also reset. The power-on sequence bypasses off-line I/O devices. The time required for a power-on sequence depends on the number of on-line I/O units.

<u>Note:</u> The following procedure must be used when applying or removing electrical power to input/ output devices:

- 1. Press the 2030 Stop key and wait for the Manual light to come on.

- 2. Set the Rate switch to the Single-Cycle position.

- 3. Press the 2030 Start key.

- 4. Turn power on or off on the I/O unit.

- 5. Set the Rate switch to the Process position.

- 6. Press the console Start key to resume operation.

This procedure ensures that the system is in a cycle in which read/write storage is not being accessed. Thus, any electrical surge on the channel that might have been caused by applying or removing power to the unit does not affect the contents of storage.

If power is removed from the last I/O unit (because maintenance is required) on a channel. the line terminators must be relocated in order to continue CPU operations. The last I/O unit on any channel must be on as long as the system is on.

#### Power-Off Key

This key removes power to the CPU and all on-line I/O units. The contents of main storage are not altered during the power-off operation. except that if a storage-read cycle has been taken (the Allow-Write indicator is on), a manual-write cycle is forced to ensure that the contents of the location just read are not lost.

I/O interruption conditions are reset when the Power-Off Key is operated. Therefore, any pending I/O interruptions are lost during a power-off operation.

The Power-Off key takes precedence over the Power-On key.

The recommended power-off procedure is:

- Press the console Stop key and wait for the Manual light to come on. (The Stop keys on the attached I/O units <u>do not</u> cause the system to enter the manual state.)

- 2. Press the Power-Off key.

#### Emergency Pull Switch

The Emergency Pull Switch removes all primary electrical power (including power to all on-line I/O units) with no regard to sequencing. The contents of storage may be altered if this switch is operated. As the name implies, the Emergency Pull Switch should be used only if necessary. This switch must be manually reset by the Customer Engineer.

The system is protected by thermal overload switches. If the temperature of the operating environment is too high, these switches drop system power. Contact the Customer Engineer whenever system power cannot be maintained.

#### System (SYS) Indicator

This indicator is normally on whenever either of the use meters is running. (See the Use Meters section.)

#### Manual (MAN) Indicator

This light indicates that the CPU clock is stopped and that no channel operation is in progress (as long as the System light is off). Several of the manual console controls are effective only when this lamp is on.

### Wait Indicator

When this light is on, the CPU clock is running but no instruction processing occurs. If an interruption occurs, processing is initiated as required by the program.

## Test Indicator

The Test light is on whenever the Address Compare, Check Control, ROS Control, or Rate switch is not set to Process (normal processing position).

#### Load Indicator

This indicator turns on when the Load key is pressed and released. It remains on until the load microprogram is successfully completed (the initial-load PSW is set into circuitry). See the Load Key section.

#### Load Key

This key is used to initialize the system. The following functions occur:

- 1. An automatic System Reset is performed.

- 2. The CPU clock is started.

- 3. The basic test microprogram is performed. This test is looped 128 times.

- 4. The clear UCW microprogram is run to reset all the flag bytes in the UCW area of auxiliary storage.

- 5. The load microprogram is begun. This routine analyzes switches G, H, and J to determine the address of the program-loading I/O device (load-unit address). When this routine is completed, the Initial Program Load (IPL) PSW has been successfully set up, and the Load light is turned off.

Note that the system mask is reset when the load key is pressed. The system mask in the IPL PSW is then effective as soon as the IPL PSW is set up.

## Interrupt Key

When this key is pressed, the interruption code of the external old PSW is altered to indicate that an external interruption is pending. The system recognizes this interruption only if programmed to do so.

Switches F, G, H, and J

These rotary switches are <u>normally</u> used by the operator for the following operations:

- 1. Manual alteration of an instruction address or a ROS address (F, G, H, and J).

- 2. Manual entry of the load-unit address (G, H, and J).

- 3. Manual entry of a byte of information into main storage or into a data-flow register (H and J).

Note: The functions of these four switches are described in detail in other sections of this manual. Switch F is also used for 1400 compatibility operations (see IBM System/360 Model 1400 Compatibility Feature, Form A24-3255). Switches F and G have particular significance for 1620 compatibility operations (see IBM System/360 Model 30, 1620 Compatibility Feature, Form A24-3365).

#### CONSOLE CONTROLS

The manual controls on the 2030 console permit the operator to initiate system operation in any of several modes, and to perform display and store operations.

<u>Note:</u> Storage Protection is not effective during main-storage alteration or display operations initiated from the console. Care must be exercised to ensure that useful data is not unintentionally altered.

## Data and Address Entry Switches

Eight rotary switches are provided for manually entering data or addresses into the system. Each of these sixteen-position switches provides one hexadecimal digit (four bits plus parity). Switches A, B, C, and D are used to enter an address for manual operations involving main or auxiliary storage, or to set up a compare address. These four switches are connected to the main-storage address register and to the compare (match) circuits. Switches F, G, H. and J are used to set up an instruction address, a ROS address, a load-unit address, or enter manual data into the system. These four switches are connected to the data-flow system through the A- and B-registers.

These switches are normally used as follows:

| Switch     | Function                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| A,B,C,D    | A stop or restart address to be<br>matched against the contents of<br>the Main Storage Data Register<br>(MSDR) or the ROS address regis-<br>ter (WX). |

| A, B, C, D | A main-storage address for manual store or display operations.                                                                                        |

| F,G,H,J    | An instruction-Start address or a ROS-Start address for a manual operation.                                                                           |

| G, H, J    | The load-unit address (I/O device<br>and channel address from which<br>the program is to be loaded).                                                  |

| H,J        | A data byte to be loaded into main<br>or auxiliary storage, or into a<br>data-flow register.                                                          |

The specific functions provided by these eight switches are detailed in various sections of this publication.

Switches F and G also have functions unique to the 1400 and 1620 compatibility features.

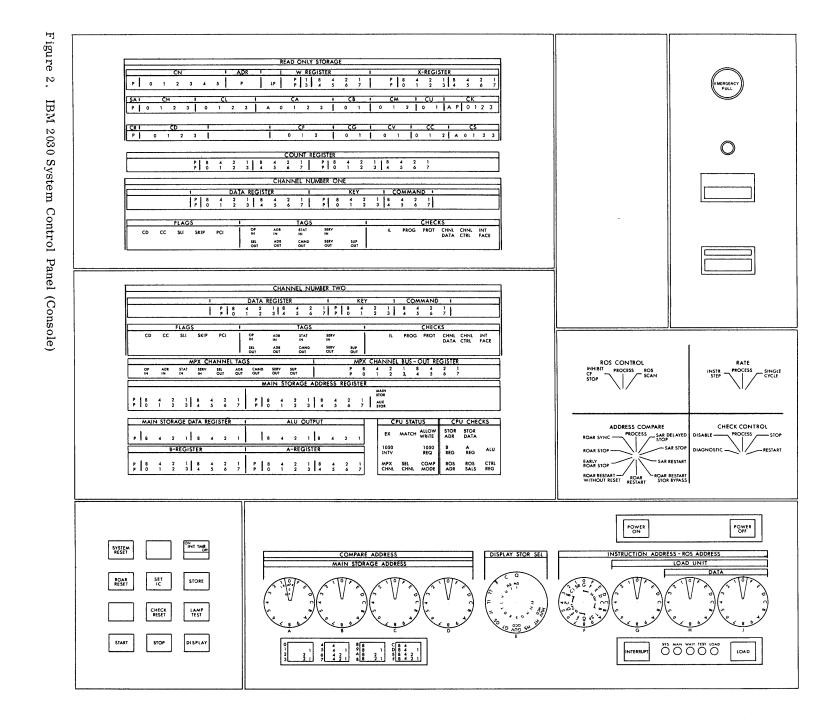

#### Display-Storage Selection Dial

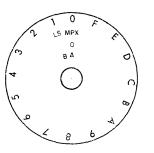

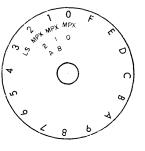

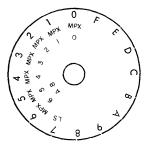

This control can be used to display information from (or store into certain) system registers that do not have full-time indicators on the console. In addition, provision is made to display from or store into any main-storage or auxiliary-storage location. The dual-concentric rotary switch labeled E is used to access the registers and system control points shown on the dial (Figure 3).

Use of the Storage-Display Selector switch is described in the Display and Store Operations section.

Figure 3. Display-Storage Selection Switch

## OPERATION CONTROLS

Four rotary control switches are provided to allow any of several modes of system operation. Although these controls are normally used only by the IBM Customer Engineer, certain of their functions are useful to the programmer and operator. The Test light is on if these four switches are not all set to the Process position.

## Rate Switch

The three modes of operation provided by this control are:

#### Instruction Step (INSN STEP) Position

When the Rate switch is in this position, one complete instruction (including all pending unmasked interruptions) is executed each time the Start key is pressed. After the instruction has been executed, the A- and B-registers contain the address of the next instruction. The stop that then occurs is identical to the stop that occurs when the Stop key is pressed.

If an input/output instruction is executed, the I/O instruction and all associated chaining is completed before the final stop occurs. If the start key is pressed again during the chaining operation, the next instruction is processed.

## Process Position

This position of the Rate switch is used for normal program processing.

## Single-Cycle Position

When the Rate switch is in this position, the system advances only one ROS cycle each time the Start key is pressed. Data overruns may occur if this mode is used for input/output operations.

#### Check Control Switch

The setting of this switch determines the system reaction when an error is detected in the CPU or I/O channels. Several courses of action are allowed as follows:

#### **Diagnostic** Position

In this mode, system control in case of an error is under control of a special microprogram.

## Disable Position

When the system is operated in this mode, parity errors are logged (in associated check circuitry), but otherwise the failure is ignored. Note, however, that certain system errors cannot be ignored; that is, automatic correction of read-only storage addressing is not provided; and the wrong word will be accessed. Results obtained while processing a problem program in this mode may be wrong.

## Process Position

This position of the Check Control switch is used for problem-program processing. When a parity check occurs, the malfunction trap microprogram is automatically initiated. This routine stores the contents of the machine check register and the program status word in fixed main-storage locations and originates a machine check interruption (refer to the IBM System/360 Principles of Operation, Form A22-6821).

#### Stop Position

Detection of a parity error in this mode causes an unconditional CPU clock stop, regardless of machinecheck masks. I/O data overruns may occur if the system is operated in this mode.

#### **Restart** Position

When an error occurs in this mode, the resultant system response is dependent upon the setting of the Address Compare switch as follows:

1. With the Address Compare switch set to SAR Restart, a System Reset is initiated, the basic micro-diagnostic and clear-UCW routines are executed, the instruction counter is set to the address specified by switches F, G, H, and J, and an instruction cycle is started.

- 2. With the Address Compare switch set to ROAR Restart or ROAR Restart Storage Bypass position, the circuitry registers (not general-purpose, floating-point, or UCWs) are reset, the ROS address register is set as specified by switches F, G, H, and J, and the resulting microprogram is initiated (with or without affecting main storage, depending on the setting of the Address Compare switch).

- 3. With the Address Compare switch set to ROAR Restart Without Reset, operation is identical to that of ROAR Restart except that no reset is initiated.

- 4. With the Address Compare switch set to any other position, the address specified by switches F, G, H, and J is placed in the instruction counter and an I-cycle is started.

#### Address Compare Switch

This switch determines whether the CPU match circuit is connected to the Read-Only Storage Address Register (ROAR) or to the Main-Storage Address Register (SAR), and the system's reaction when an address match occurs. When the switch is in any position that contains the term ROAR, the read-only storage address register is compared to switches A, B, C, and D; other positions apply to the main-storage address register. The switch positions and the associated system responses are as follows:

#### Process Position

This position is used for normal problem-program processing.

## ROAR SYNC Position

This position provides a sync pulse (for Field Engineering purposes) when the address specified by switches A, B, C, and D matches the contents of the read-only storage address register (WX register).

#### **ROAR Stop Position**

With this setting, system operation proceeds until the contents of the ROAR match the address specified by switches A, B, C, and D. When this match occurs, the CPU clock is turned off (at the end of the ROS cycle in progress) and the system stops.

#### Early ROAR Stop Position

With this setting, processing proceeds until the contents of the ROAR match the address specified by switches A, B, C, and D. When the match occurs, the CPU clock is turned off (at the end of the current ROS cycle) and the system stops. The ROAR indicators display the address of the ROS word just prior to the ROS word-address set in switches A, B, C, and D. The ROS word displayed, however, is the one at the address specified in switches A, B, C, and D.

ROAR Restart ROAR Restart Without Reset, and ROAR Restart Storage Bypass Positions

These three settings are similar in that the occurrence of a match between a ROAR address and switches A, B, C, and D causes the ROAR to be reset to the value specified by switches F, G, H, and J. In no case are the general-purpose or floating-point registers, or the UCW flag bytes reset.

For ROAR Restart, CPU registers are reset before the ROAR is reset.

For ROAR Restart Storage Bypass, the function is identical except that main storage is not permitted to operate; hence, normal problem-program processing cannot be done in this mode.

In the ROAR Restart without Reset position, the function is the same as with ROAR Restart except that no reset is performed.

## SAR Restart Position

When a match occurs in this mode, a fixed address is forced into the ROAR. The basic micro-diagnostic and clear-UCW routines are performed, the address specified by switches F, G, H, and J is loaded into the instruction counter, and an instruction cycle is started.

## SAR Stop Position

When a match between the SAR and switches A, B, C, and D occurs in this mode, the CPU clock is stopped at the end of the write cycle in which the match occurs.

## SAR Delayed Stop Position

In this mode, a match between the SAR and switches A, B, C, and D causes the CPU clock to stop at the

conclusion of execution of the instruction in which a match occurs. All pending interruptions are taken before the clock stops.

### **ROS Control Switch**

This switch is primarily for Field Engineering use.

#### **ROS Scan Position**

This mode is used when certain diagnostic tests (scan ROS or read/write storage) are run.

#### Inhibit CF Stop Position

In this mode, processing occurs in the normal fashion except that microprogram stops (determined by the CF field) are ignored.

#### **Process Position**

This position is used for normal program processing.

#### PUSH BUTTONS

Several push button switches are provided to allow the operator to perform manual operations or to initiate system functions. The title given to each button describes the resulting function when the switch is operated.

Power-On Key, Power-Off Key, and Emergency Pull Switch

These controls are discussed in the Operator's Control Panel section.

#### System Reset Key

Pressing this key resets the CPU clock, all registers (except the general-purpose and floating-point registers in local storage), the controls in the CPU, and all I/O units (including all sense and status for the I/O units). In addition, when the Start key is pressed after operation of the System Reset key, the Basic Test and UCW Reset microprograms are initiated. (The Basic Test routine is looped 128 times, so disregard the various error indicators during this time.) See the ROAR Reset Key section.

Also, when the System Reset key is operated, the current system mask is reset. However, upon restart, the same current system mask controls the system if that mask in local storage has not been altered before restart (see <u>Current Program Status</u> Word Selection section).

#### **ROAR Reset Key**

This key is used to manually alter the ROAR address (WX registers) from the contents of switches F, G, H, and J. The ROAR Reset key is active only when the CPU clock is stopped; its function is initiated when the Start key is pressed.

If the ROAR Reset key is pressed after a System Reset function but before the Start Key is pressed, the Basic Test and Clear UCW microprograms are <u>not</u> initiated, that is, the UCW flag bytes in the MPX storages are not reset to zeros.

#### Start Key

If the Start key is pressed after a normal stop (for example, after the Stop key is pressed), instruction processing continues as if no stop had occurred. Machine status is unaffected.

If the Start key is pressed after a Start Reset function, the Basic Test routine is performed, and the Clear UCW routine resets all UCW flag bytes to zeros. If the Start key is operated again, the PSW located at address 0000 is loaded into circuitry, and processing starts. (See <u>Start Reset Key</u> and <u>ROAR</u> Reset Key sections.)

## Set IC Key

This key is used to manually alter the Instruction Counter (IC) address from the contents of switches F, G, H, and J, and is active only when the CPU clock is stopped (Manual light is on). When the Set IC key is pressed, the altered instruction address is displayed in the B- and A-registers, and the system stops. Any outstanding channel share cycles are completed before this microprogram stop occurs. Processing begins at the new instruction address when the Start key is pressed.

If the Set IC key is pressed after a System Reset function, the instruction counter is set to the address entered from switches F, G, H, and J.

#### Check Reset Key

This key resets all machine-check logic circuits. The Check Reset key may be used at any time (CPU clock running or stopped). When this key is pressed, the system enters the stopped state when:

- 1. The instruction being processed has been completed,

- 2. All pending interruptions have been serviced, and

- 3. Any I/O operation in progress has been finished.

If data or command chaining is involved, it is completed before the CPU clock is stopped. The System light stays on as long as any I/O unit (except the 1050) is engaged in an I/O operation; that is until device-end is accepted for the last command in a chain for that I/O device).

Note that the machine environment is not destroyed and the program that was in progress can be restarted (by operation of the Start key). The address of the next instruction is displayed in the B- and A-registers.

When the system is in the stopped state, the multiplexor channel is allowed to accept sharerequest traps (microprogram branches), and the selector channel is allowed to accept data cycles. This provision permits input-terminal and multisystem operations even though the 2030 program in progress has been manually interrupted.

Even though these operations are in progress, data can be stored or displayed. At the instant a cycle is being used for a channel operation, the manual store and display circuits are inactive. However, if the Store or Display key is <u>held</u> operated, the data is stored or displayed. If the store key is operated only during a channel-operation cycle, the data to be manually stored is not stored. It is advisable, therefore, to display any location (in which data is manually stored) so that storing can be verified.

#### Interval Timer Switch (INT TMR)

When the Interval Timer feature is installed and this switch is on, the interval timer is allowed to generate program interruptions. If the switch is off, the interval timer is ignored and the mainstorage timer locations are not changed.

#### Store Key

This key causes the hexadecimal byte specified by switches H and J to be entered into the area selected by the Display Storage Selection dial (switch E).

If a register is selected by switch E, the data byte is entered into that register and displayed in both the B- and A-registers. Information cannot be stored in all the registers selectable by switch E. See the Store and Display Section.

When main storage (MS) or auxiliary storage (AS) is selected by switch E, switches A, B, C, and D specify the address into which the data byte is stored. The data byte (from switches H and J) is displayed in both the B- and A-registers.

The CPU clock must be stopped for the store operation. If main or auxiliary storage is being accessed, the Allow Write light must be off.

#### Lamp Test Key

Pressing this key causes all indicator lights on the 2030 console to turn on. This test does not affect system operation and can be performed during program execution if desired. (The console lamps will be slightly dimmer than during normal operation.)

#### Display Key

The function of this key is similar to that of the Store key, except that the accessed location is not altered. The Display key is provided so that registers that do not have their own console indicators can be displayed.

Main-storage (MS) and auxiliary-storage (AS) locations are displayed by setting switch E to the storage area desired, and switches A, B, C, and D to the address of the location to be displayed. The Main Storage Data Register (MSDR) is used to display the contents of the accessed storage location. If the original value in the MSDR will be needed when the program is restarted, record this value so the MSDR can be restored after the display operation. If the ROS control, Rate, Address Compare, and Check Control switches are all set to Process, and the system is allowed to come to a normal stop (Stop key was pressed and the manual light is on), the contents of the MSDR <u>need not</u> be restored before the Start key is pressed to resume program operation.

|     |   |    |    |     | _      | _      |    |    |        |            |            |            | R       | EAD    | 0          | VLY    | STO    | ORA         | GE     |        |         |        |     |        |     |        |        |        |            |               |     |           |            |        |

|-----|---|----|----|-----|--------|--------|----|----|--------|------------|------------|------------|---------|--------|------------|--------|--------|-------------|--------|--------|---------|--------|-----|--------|-----|--------|--------|--------|------------|---------------|-----|-----------|------------|--------|

|     |   |    | С  | N   |        |        |    | T  | 7      | <b>D</b> R |            | 1          | 1       |        | W          | REG    | GIST   | TER         | _      |        |         | T      |     |        |     |        | X      | -REC   | <u>SIS</u> | ER            |     |           |            |        |

| Р   | 0 | 1  | 2  | ?   | 3      | 4      | 5  |    |        | P          |            | LP         |         |        | P<br>P     | 1<br>3 | 8<br>4 |             | 4<br>5 | 2<br>6 | 1<br>7  | 1      |     | P<br>P |     | 8<br>0 | 4      | 2      |            | $\frac{1}{3}$ |     | 4<br>5    | 2<br>6     | 1<br>7 |

| SAI |   | C  | H. |     | 1      |        |    | Cι |        |            | 1          |            |         | C      | A          |        |        |             |        | C      | 3       | 1      |     | C      | M   |        | T      | Ċυ     |            | 1             |     | Сĸ        |            |        |

| Р 🖠 | 0 | 1  | 2  | 3   | ·      | 0      | 1  |    | 2      | 3          |            | A          | 0       |        | 1          | 2      | 3      |             |        | 0      | 1       | Ι      | 0   |        | 1   | 2      | I      | 0      | 1          | A             | Р   | 0         | 12         | 3      |

|     |   |    |    |     |        |        |    |    |        |            |            |            |         |        |            |        |        |             |        |        | _       |        |     |        |     |        |        |        |            |               |     |           |            |        |

| CRI |   |    | CD |     |        | 1      |    |    |        |            |            | 1          |         |        | CF         |        |        |             |        | C      | 3       | 1      |     | C١     | /   |        |        | CC     |            | 1             |     | CS        | 5          |        |

| P   | ( | C  | 1  | 2   | 3      | 1      |    |    |        |            |            |            |         | 0      | 1          |        | 2      |             |        | 0      | 1       | 1      |     | 0      | 1   |        | 0      | 1      |            | 2             | A ( | 0 1       | 2          | 3      |

|     |   |    |    |     |        |        |    |    |        |            |            |            |         |        |            |        |        |             |        |        |         |        |     |        |     |        |        |        |            |               |     |           |            |        |

|     |   |    |    |     |        |        |    |    |        |            |            |            |         | со     | UN         | R      | EGI    | STE         | R      |        |         |        |     |        |     |        |        |        |            |               |     |           |            |        |

|     |   |    |    |     | P<br>P | 8<br>0 | 4  |    | 2<br>2 | 1<br>3     | 1          | 8 4<br>4 5 |         | 2<br>6 | 1<br>7     | 1      | P<br>P |             | 8<br>0 | 4<br>1 | 2<br>2  | 1<br>3 |     | 8<br>4 | 4   |        | 2<br>6 | 1<br>7 |            |               |     |           |            |        |

|     |   |    |    |     |        |        |    |    |        |            |            | 0          | ΉÁ      | NN     | IEL        | NŪ     | MBE    | ER          |        | E      |         |        |     |        |     |        |        |        |            |               |     |           |            |        |

|     |   |    |    |     | 1      |        |    |    | ۲AC    | AP         | FG         | ISTER      |         |        |            | -      |        |             |        | K      | Y       |        | _   |        | 201 | MM     |        | DI     |            |               |     |           |            |        |

|     |   |    |    |     | P      | 8<br>0 | 4  |    | 2 2    | 1          | I          | 8 4<br>4 5 |         | 2<br>6 | 1<br>7     | Ì      | P      |             | 8<br>0 | 4      | 2       |        | 1 3 | 8<br>4 | 4   | t I    | 2<br>6 | ;      |            |               |     |           |            |        |

|     |   |    |    |     |        |        | _  |    |        |            |            |            |         |        |            |        |        |             |        |        |         |        |     |        |     |        |        |        |            |               |     |           |            |        |

|     |   |    | FL | AG  | S      |        |    |    | Ī      |            |            |            |         |        | TA         | GS     |        |             |        |        |         | 1      |     |        |     |        |        | CHEC   | CKS        |               |     |           |            |        |

| с   | D | сс | ş  | 511 | sk     | (IP    | PC | I  |        | i<br>I     | DP<br>N    | A<br>IM    | DR<br>ł |        | STA<br>IN  | T      |        | SERV<br>IN  |        |        |         |        |     | IL     | _   | PRO    | 3      | PROT   |            |               |     | INL<br>RL | INT<br>FAC |        |

|     |   |    |    |     |        |        |    |    |        | 5          | SEL<br>DUT |            | DR      |        | CMN<br>OUT |        |        | SERV<br>OUT |        | SL     | Р<br>JT |        |     |        |     |        |        |        |            |               |     |           |            |        |

Figure 4. Console Display Indicators (Part 1 of 2)

A register selected by switch E is displayed in the A-register. When either the I- or J register (see Figure 8) is selected, both the I- and J-registers are displayed in the Main Storage Address Register (MSAR). This is also true for the U- and V-registers (see Figure 8). (The selected register is also displayed in the A-register.)

The CPU clock must be stopped and the Allow Write indicator must be off for any display operations involving storage, or for displays of the IJ or UV registers. Note, however, that the contents of the I-, J-, U-, or V-registers can be displayed in the A-register if the Allow Write indicator is on.

## DISPLAYS

Several indicators are provided to display control information, data bytes, and system status. Each indicator shows the binary condition of a latch or signal line. When a latch is set, or a signal is on, its associated lamp is lighted. In cases where the position of a bit in a field is important, the numerals 0, 1, 2, 3, etc, are lighted; but where bits are grouped to form a numeric digit, the binary bit values are lighted (8,4,2,1). The <u>P</u> lamps associated with many of the console displays represent the parity bit for the information. In addition to the control information provided by the read-only storage display, the 2030 console displays the contents of certain data registers, the read/write storage address register, a number of CPU status conditions, the multiplexor channel tags, and several check conditions. Although only some of the registers are displayed, provision is made to display the contents of all CPU registers as described in the Display, and Store section of this publication.

## **CPU** Status Indicators

The CPU status indicators (Figure 4, Part 2 of 2) signal the actual operating status of the CPU at any time. These indicators and their corresponding meanings are:

EX. This lampturns on at the end of each instruction execution (that is, whenever the micro-instruction branch-on-interrupt occurs). In the microinstruction word immediately following the interrupt word, the EX latch is reset. Note that if the system is programmed to stop at the end of instruction execution (for example, if the stop button has been pressed), the EX lamp remains on. It turns off when the CPU clock is restarted.

|        |         |     |          |        |            |         |          |        |           |         |        |               |        | CH                      | IAN    | NNEL       | N      | IMB    | ER T                      | WC | )      |        |   |                             |               |            |          |        |           |            |        |              |             |

|--------|---------|-----|----------|--------|------------|---------|----------|--------|-----------|---------|--------|---------------|--------|-------------------------|--------|------------|--------|--------|---------------------------|----|--------|--------|---|-----------------------------|---------------|------------|----------|--------|-----------|------------|--------|--------------|-------------|

|        |         |     |          |        |            |         |          | 1      |           |         | D      | DAT           | A R    | ĒGI                     | STE    | R          |        |        | 1                         |    |        | KE     | Ŷ |                             | I             |            | co/      | MM     | AND       |            | i _    |              |             |

|        |         |     |          |        |            |         |          |        | P<br>P    | 8<br>0  | 4      |               | 2<br>2 | $\frac{1}{3}$           | 8<br>4 | 4<br>5     | 2<br>6 |        |                           |    | 8<br>0 | 4      |   | 2<br>2                      | $\frac{1}{3}$ | 8<br>4     |          | 4<br>5 | 2<br>6    | 1<br>7     |        |              |             |

|        |         |     |          |        | FLAG       | S       |          |        |           |         | 1      |               |        |                         |        | Ť,         | AGS    |        |                           |    |        |        |   |                             |               |            |          | c      | HEC       | ĸs         |        |              |             |

|        | C       | CD  | с        | с      | SLI        | S       | KIP      |        | PCI       |         | H<br>S | DP<br>N<br>EL |        | ADR<br>IN<br>ADR<br>OUT |        | ii<br>c    |        |        | SERV<br>IN<br>SERV<br>OUT |    | SUI    |        |   |                             | IL            | P          | ROG      | P      | ROT       | CHN<br>DA1 |        | CHNL<br>CTRL | INT<br>FACE |

| _      | -       |     |          |        |            | MPX     | Ci       | IAL    | INE       | L T     | AGS    |               |        |                         | -      |            | _      |        |                           |    |        | VPX    | C | HAN                         | INE           | BL         | JS -     | OU     | JT RE     | GIST       | TER    |              |             |

|        | C<br>II |     | AD<br>IN |        | STAT<br>IN | S<br>II | ERV<br>N |        | EL<br>DUT | AI<br>O |        | CMN           |        | SERV<br>OUT             |        | SUP<br>OUT |        |        | _                         |    | P<br>P | 8<br>0 |   | 4<br>1                      | 2<br>2        | 1<br>3     | 8        |        | 4<br>5    | 2<br>6     | 1<br>7 |              |             |

|        |         |     |          |        |            |         |          |        |           |         |        |               | MA     | IN                      | ST     | ORAC       | E A    | DD     | RESS                      | RE | GIS    | TER    | 2 |                             |               |            |          |        |           |            |        |              |             |

| P<br>P |         | 3   | 4        | 2      | 1<br>3     | 84      |          | 4<br>5 | 2<br>6    | 1       |        | P<br>P        | 8      |                         | 4      | 2          | 1<br>3 | 8<br>4 | 4<br>5                    |    | 2<br>6 | 1<br>7 |   | MAIN<br>STOR<br>AUX<br>STOR |               |            |          |        |           |            |        |              |             |

|        | м       | AIN | ST       | ORA    | GE [       |         | RE       | GIS    | STE       | R       | 1      |               |        |                         | A      | ALU (      | OUTI   | νUT    |                           |    |        |        |   |                             | CI            | <u>v s</u> | STAT     | US     |           |            | CPL    | J ČHE        | CKS         |

| P      | 8       | 3   | 4        | 2      | 1          | 8       |          | 4      | 2         | 1       |        |               | 8      |                         | 4      | 2          | 1      | 8      | 4                         | :  | 2      | 1      |   |                             | EX            | ма         | тсн      |        | LOW       | STC<br>AD  |        | STOR<br>DATA |             |

|        |         |     |          | B-F    | REGI       | STEI    | 2        |        |           |         | 1      |               |        |                         | A      | -REC       | GIST   | ER     |                           |    |        | 티      |   |                             | 050<br>ITV    |            |          |        | 050<br>EQ | B<br>REG   | 3      | A<br>REG     | ALU         |

| P<br>P |         | 3   | 4        | 2<br>2 | 1          | 8       |          | 4<br>5 | 2<br>6    | 1<br>7  |        | P             | 8      |                         | 4      | 2          | 1      | 8      | 4                         | :  | 2      | 1      |   |                             | PX<br>HNL     | SE         | L<br>INL |        | OMP       | RO         |        | ROS<br>SALS  | CTRL<br>REG |

Figure 4. Console Display Indicators (Part 2 of 2)

Match. Some modes of operation require the use of an exclusive OR match circuit. The match indicator turns on whenever the compare address in switches A, B, C, and D matches the contents of either the Main Storage Address Register (MSAR) or the Read-Only Storage Address Register (ROAR). The position of the address-compare switch determines which of these registers is monitored, as well as the system response to a match.

<u>Allow Write</u>. Whenever the allow-write indicator is on, main or auxiliary storage has completed a read operation, but not the corresponding write operation. When this indicator is on, manual display and store operations of main or auxiliary storage are not possible.

1050 INTV. This indicator is turned on when an addressed IBM 1050 system device requires manual intervention (out of cards, out of forms, etc). The light is turned on only if the device was in run mode at the time the intervention became necessary. The 1050 INTV light is turned off when the unit has been made ready and when that unit is re-addressed, or by the 2030 System Reset or Load keys.

1050 REQ. This light turns on whenever the operator presses the request key on the 1052. It is reset when attention status is recognized by the attachment and accepted into the unit status register.

MPX CHNL. Whenever a multiplexor channel share request is recognized by the CPU, this light turns on. This light turns off at the completion of the share cycle.

SEL CHNL. This lamp is lighted whenever either selector channel is using the read-only storage (such as for a selector-channel chaining operation).

<u>COMP MODE</u>. Whenever the system is operating in compatibility mode, this light is on. This lamp is turned on at the same time as the W3 lamp (the W-register read-only-storage display bit-3 position position--see Part 1 of Figure 4). In the central processing unit are several check circuits. Whenever a check is detected, a check latch is set. and a bit is turned on in the machinecheck (MC) register, as follows:

| MC Register | × •• ••                 |

|-------------|-------------------------|

| Position    | Indication              |

| 0           | A-REG                   |

| 0<br>1      | B-REG                   |

| 2           | STOR ADR                |

| 3           | CTRL REG                |

| 4           | ROS SALS (Read-Only     |

|             | Storage Sense Amplifier |

|             | Latches)                |

| 5           | ROS ADR                 |

| 6           | STOR DATA               |

| 7           | ALU                     |

|             |                         |

Except for the ALU check, the turning on of any of these lights is an indication of detected bad parity in the associated register. In the ALU, a duplicate check is made because the ALU does not use the parity bit (input is complemented and the operation is performed in both uncomplemented and complemented form, and the answers are compared). When the CPU stops during normal program processing with any one or more of these indicators on, call the Customer Engineer.

#### Registers

The following registers have full-time indicators on the 2030 console (left center and upper left portions of the console, Figure 3).

The ALU Output is not a register but is listed here because of its relationship with the actual registers.

B- and A-Register Displays

These indicators provide full-time display of the contents of the B- and A-registers.

During manual operations, the display from the A-register depends on the settings of console switches (see the Display Key section).

When the system is in the Wait state (instruction processing stopped and the program is waiting for an interruption) or when in the process-stop condition (such as when the Stop key is pressed), the instruction counter (IC) is displayed in the B-register (I-register contents) and the A-register (J-register contents).

#### Main-Storage Data Register (MSDR) Display

For CPU or multiplexor-channel operations, these indicators display information being transferred to or from either main or auxiliary storage. The MSDR indicators, therefore, provide full-time display of the contents of the R-register.

For manual operations, the MSDR indicators display the data byte being stored, displayed, etc., depending upon the setting of 2030 console switches.

#### ALU Output Display

These indicators provide full-time display of the output of the arithmetic-logic unit (ALU).

#### MAIN STOR Indicator

When on, this light (located to the right of the MSAR lamps) indicates that a main-storage address is being displayed by the MSAR lights.

#### AUX STOR Indicator

When on, this light (located to the right of the MSAR lamps) indicates that an auxiliary-storage address is being displayed by the MSAR lights.

Main Storage Address Register (MSAR) Display

When the MAIN STOR indicator is on during normal processing operations these lights display the address of the main-storage location being accessed.

During manual operations, the information displayed in the MSAR lights may apply to any of several internal system registers, depending upon the setting of the Display Storage Selection dial (switch E) and/or rotary switches A, B, C, and D.

When the AUX STOR indicator is on, the highorder hexadecimal digit (four high-order bits) of the MSAR specify which part of auxiliary storage is addressed (that is, local storage or one of the MPX storages).

Note that when the system is in Wait state or in the process-stop condition, the address of the next instruction to be executed (instruction counter--IC) is displayed in the B- and A-registers. The operation code is not displayed. MPX Channel Bus-Out Register

These lights indicate the byte of information being sent from the main-storage data register (MSDR) to the multiplexor channel.

## MPX Channel Tags

These lights provide display of the current status of various multiplexor-channel I/O interface control lines.

OP IN. The operational in (OP IN) lamp indicates that an I/O unit is selected and is in communication with the channel.

<u>ADR IN</u> The address in (ADR IN) light indicates that the address of the currently selected I/O unit is on bus-in. (<u>Bus-in is the data and control</u> transmission network for information transfer from a control unit to the CPU.)

STAT IN. The status in (STAT IN) light indicates that the selected I/O unit has placed status information on bus-in.

SERV IN. The Service in (SERV IN) light indicates that the selected I/O unit is ready to send or receive data.

<u>SEL OUT</u>. The select out (SEL OUT) light indicates that the various I/O units attached to the multiplexor channel are being polled to determine whether any device requests service.

ADR OUT. The address out (ADR OUT) light indicates that address information is on bus-out. (Busout is the data and control information network from the CPU to the control unit.)

<u>CMND OUT</u>. The command out (CMND OUT) light indicates that the information on bus-out is a command.

SERV OUT. The service out (SERV OUT) light indicates that the CPU has accepted the information on bus-in or has provided data on bus-out.

<u>SUPP OUT</u>. The suppress out (SUPP OUT) light indicates that status and data transfers are suppressed, that command-control chaining is in progress, or that a malfunction (selective) reset is being effected with regard to the selected I/O unit. Several indicators are provided for each selector channel. The Channel Number One lights refer to selector-channel one; the Channel Number Two lights refer to selector-channel two.

The Count Register (located above the Channel Number One lights) is used to observe the current byte count for selector-channel one (switch E set to GUV-GCD) or selector-channel two (switch E set to HUV-HCD).

## Data Register

Whenever.a main-storage share cycle is initiated by a channel, these lights provide full-time display of information being transferred.

## Key

These lights provide full-time display of the mainstorage (CAW) protection key for all commands associated with the Start I/O instruction.

## Command

The four low-order bits of the CCW operation code are displayed by these lights.

## Flags

This group of five indicators displays the manner in which a channel command should be executed, as follows:

CD. This light indicates chaining of data addresses.

CC. This light indicates command chaining.

<u>SLI.</u> This light (suppress-length indication) indicates that the program will <u>not</u> be notified in the event of a wrong-length record.

SKIP. This light specifies suppression of information-transfer to storage during a read, read backward, or sense operation.

<u>PCI</u>. This light (program-control interruption) indicates that the channel will generate an interruption condition when the CCW takes control of the channel.

#### Selector-Channel Tags

The nine tag indicators for each selector channel perform the same functions as the corresponding indicators for the multiplexor channel (see  $\underline{MPX}$  Channel Tags section).

## Selector-Channel Checks

Each selector channel has a number of check circuits that continually monitor channel operation. When a malfunction is detected, the appropriate check light is turned on. These checks are:

<u>IL</u>. If the SLI flag is <u>not</u> on, this light (incorrect length condition) is turned on when the number of bytes in the assigned storage area is not equal to the number of bytes requested or offered by the I/O unit.

PROG. This light (program check) indicates that the channel has detected a programming error.

<u>PROT.</u> This light (protection check) indicates that the channel attempted to violate a portion of main storage that is protected for the current operation.

<u>CHNL Data.</u> This light (channel data check) indicates that the channel has detected a parity error in the information transferred to or from main storage during an I/O operation.

CHNL CTRL. This light (channel control check) indicates that a machine malfunction affecting channel controls has occurred.

INT Face. The interface control check is caused by sequencing problems on the I/O interface.

## Read-Only Storage Displays

In general, these indicators are for Customer Engineering use. Therefore, only a short description of each ROS field is presented here.

CA, CB, CC, CF, CG, CV. These fields control operation of the ALU.

<u>CD.</u> This field selects one of the several system registers to receive the output of the ALU. A given register can be used as both the source and destination during a single ROS cycle. <u>CK.</u> This field provides a source of data and control bits (that is, generates constants).

<u>CM</u>, <u>CU</u>. These two fields control storage operation. They determine which storage area (main or auxiliary) is to participate in a particular read or write operation.

CN, CH, CL. These fields control the address of the next ROS word.

LP. This light indicates that the air pressure in the read-only storage unit is low, or that the temperature of main storage is below the optimum operating range.

W- and X-Register. These indicators display the address of the ROS word just read.

<u>CS.</u> This field supplies status indications to various machine control points.

## USE METERS

The 2030 console has two direct-reading meters that measure operating time: a customer's meter and a Customer Engineer's meter. The position of a key switch determines whether the customer's meter or the CE meter is operating. The Customer Engineer holds the key for this switch; and whenever he is performing either scheduled or unscheduled maintenance in the CPU, he will set the switch to cause the CE meter to operate. One of these meters (determined by key-switch setting) operates whenever the CPU clock is running and either:

- 1. The CPU is not in the wait state or,

- 2. There is an interruption pending, or

- 3. A manual store or display operation is in progress. The System indicator is on when either meter is running. It indicates that some productive activity is in progress. The System light stays on as long as any I/O unit (except the 1050) is engaged in an I/O operation (that is until device-end occurs for the last command in a chain for that I/O device). This can occur after the Stop key is pressed.

The use meter (customer or CE) operates for a minimum of 400 milliseconds each time it is started.

## SYSTEM POWER-ON AND POWER-OFF

Power to all system units is brought up during a system power-on sequence. If power cannot be successfully brought up on an I/O unit that is online to the CPU, the system power-on sequence cannot be completed. See the Operator's Control Panel section.

## PROGRAM LOAD ROUTINE

Prepare the I/O unit from which the program is to be loaded as follows. (Refer to the appropriate Systems Reference Library publication for information concerning the particular I/O unit involved.)

## Card I/O Unit Preparation

When the program to be loaded is contained in punched cards, a card reader must be initialized. The following steps generally apply to all card readers:

- Run the cards out of the read feed by performing a nonprocess runout as described for the particular card reader.

- Place the program-load deck in the read-feed hopper.

- Press the reader start key.

The card reader is now ready to read the program deck.

#### Disk I/O Unit Preparation

When the program is to be loaded from a magnetic disk unit:

- Turn the disk-drive meter switch on. This allows the device to be used for input/output.

- Place the disk pack containing the desired program on the disk drive and operate the disk-drive start key.

The disk storage unit is ready when its ready light is on.

## Tape I/O Unit Preparation

When a magnetic tape unit is being used to load the problem program:

- Open the tape unit door for access to the tape reels and read/write assembly.

- Place the tape reel containing the program on the left reel hub and lock it in place.

- Thread the tape along the tape path and onto the take-up reel.

- Wind the tape until the load-point marker is well past the read/write head.

- Close the access door.

- Press the load-rewind key.

The tape unit is now ready to be used as input when called on by the program-load routine.

## Console Operation (Program Loading)

With the system power on and the appropriate I/O load unit set up:

- 1. Set the address of the I/O load unit that contains the program to be loaded in rotary switches G, H, and J (see Figure 2, OCP section). The channel address is set in switch G; the unit address in switches H and J.

- 2. Make sure that the ROS Control, Rate, Address Compare, and Check Control switches are all in the PROCESS position (see Figure 2, right center section). The Test light on the OCP portion (see Figure 2) of the 2030 console is off only when all four of these switches are in the PROCESS position.

- 3. Press the Load key on the OCP portion of the 2030 console. The Load light (see Figure 2, OCP section) turns on when the Load key is pressed, and it turns off after the load routine has been completed (when the loading of the new PSW has been completed).

A system reset is initiated when the Load key is pressed. The Basic Test microprogram is looped 128 times. A microprogram (ROS) then automatically resets the UCW's in the multiplexor storages. It may or may not be necessary to clear the contents of core storage into which the new program is loaded; this is dependent upon the program.

After the program has been loaded, processing will proceed immediately unless the program loaded is written in such a manner as to prevent this. Therefore, system operating procedures and the program determine what subsequent action is to be taken. If the system is programmed to go to the wait state after the program has been loaded, operating procedures may indicate that the following action is to be initiated:

- 1. Press the Stop key to enter stopped state (Manual light on). Wait for the system light to turn off.

- 2. Load an instruction address from rotary switches F, G, H, and J into IC (Instruction Counter) by using the set-IC key (see IC in the Push buttons section of this publication).

- 3. Press the start key to start processing at the instruction address loaded.

## DISPLAY INFORMATION FROM STORAGE

The contents of any byte of storage can be displayed when the CPU clock is stopped (the Manual light on the OCP is on) and the Allow-Write indicator (in CPU status section of 2030 console--Part 2 of Figure 3) is off. The Allow-Write indicator, when on, indicates that a read-from-storage operation has been completed but that the associated write cycle has not been performed.

## Procedure

The contents of any storage position can be displayed when the following procedure is used (assume that the test light is out and normal program processing is in progress):

- 1. Press the stop key (lower left portion of 2030 console--Figure 2). The system stops after the current instruction is processed, and all pending interrupts have been serviced.

- 2. After the system stops, the allow-write indicator is off and the manual light is on.

- 3. Set the rotary display-storage-select switch (switch E) to the MS or AS position (depending upon whether Main Storage or Auxiliary Storage is to be used in this operation). (See lower portion of Figure 2.)

- 4. Place the address of the desired byte in rotary switches A, B, C, and D (Figure 2).

Note: If a byte of auxiliary storage is to be displayed, set rotary switch A to LS (for Local Storage) or to the desired MPX (multiplexor) storage position. If auxiliary is used, the address of the desired byte is then set in switches C and D.

- 5. Press the display key (lower left section of Figure 2).

- 6. Make sure that the appropriate indicator, MAIN STOR (main storage) or AUX STOR (auxiliary storage), is on. These indicators are just to the right of the main-storage address register display (see Part 2 of Figure 3).

- The address of the accessed location is then displayed in the main-storage address register (Part 2 of Figure 3). Make sure this is the address desired. (You may inadvertently have set up rotary switches A, B, C, and D incorrectly.)

- 8. The data stored in the addressed location is displayed in the main-storage data register indicators on the 2030 console.

- 9. When the system and wait lights are on and the stop key does not allow a display of storage, the operator should set the rate switch to SINGLE-CYCLE to turn off the system light and turn on the manual light.

- 10. Only when all the preceding nine items fail, should system reset be performed.

### STORE INFORMATION INTO STORAGE

Store operations are similar to display operations. That is, the contents of any position of storage can be altered if the allow-write indicator is off and the manual light is on (CPU clock stopped). If the allow-write indicator is on or the manual light is off, the store key (on OCP section of 2030 console, see Figure 2) is interlocked so that the contents of storage cannot be altered.

#### Procedure

To store a byte into storage:

1. When the system stops (stop key has been pressed), the allow-write indicator is off and the manual light is on.

- 2. Select the area of storage (to be altered) with the rotary display-storage-selection switch (switch E). Use the MS position for storing into Main Storage and the AS position for storing into Auxiliary Storage (see lower section of Figure 2).

- 3. Set the address of the selected byte of storage into rotary switches A, B, C, and D.

Note: If you are going to store a byte into auxiliary storage, set rotary switch A to LS (for Local Storage) or to the desired MPX (multiplexor storage) position. Then set switches C and D to the address to be used in auxiliary storage.

- 4. Set the byte of information to be stored in rotary switches H and J (hexadecimal representation of byte).

- 5. Press the store key (see Figure 2, lower left portion).

- 6. The data byte to be stored is displayed in the main storage data register indicators on the 2030 console. The address at which the displayed byte is stored is displayed in the main-storage address register indicators (see Part 2 of Figure 3). Check these indicators to make sure the correct data is entered onto the desired location.

## Addressing Bytes of Auxiliary Storage

In most instances, you will have no need to store or display in auxiliary storage. The following descriptions, however, are provided here for reference. The other areas of auxiliary storage are not applicable to operator use, or not used, or used only in special situations (such as for compatibility modes). Follow the appropriate procedure as described in the <u>Display Information</u> from Storage and Store Information in Storage sections. Use this section to determine the address of a particular location in auxiliary storage.

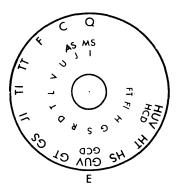

1. Set rotary switch A to the desired area of auxiliary storage (Figure 5):

Figure 5. Rotary Switch A

| Switch A Setting | Auxiliary Storage Accessed                                   |

|------------------|--------------------------------------------------------------|

| MPX 0            | Multiplexor Channel Unit Con-<br>trol Words 0 through 31     |

| MPX 1            | Multiplexor Channel Unit<br>Control Words 32 through 63      |

| MPX 2            | Multiplexor Channel Unit<br>Control Words 64 through 95      |

| MPX 3            | Multiplexor Channel Unit<br>Control Words 96 through 127     |

| MPX 4            | Multiplexor Channel Unit<br>Control Words 128 through<br>159 |

| MPX 5            | Multiplexor Channel Unit Con-<br>trol Words 160 through 191  |

| MPX 6            | Multiplexor Channel Unit Con-<br>trol Words 192 through 223  |

| LS               | Local Storage                                                |

Note: The MPX 0 setting is on all 2030 consoles. The MPX 1 and MPX 2 settings are on all 2030's that have 16K or more main-storage addresses. MPX 3, MPX 4, MPX 5, and MPX 6 settings are on 2030's (with 32K or more main-storage addresses) that have the 224 subchannel special feature.

2. Set rotary switch B to 0.

3. Set the desired byte address in rotary switches C and D as described in the following sections.

General-Purpose Register Selection

General-purpose registers 0 through 15 are selected by setting switch C to the corresponding hexadecimal equivalent (0 for register 0, F for register 15).

The desired byte in the selected general register is specified by switch D (bytes 0 through 3 by switch positions 0 through 3).

Floating-Point Register (Special Feature) Selection

Floating-point registers 0, 2, 4, and 6 are selected by setting switch C to 0, 2, 4, or 6, respectively.

The desired byte in the selected floating-point register is specified by switch D as follows:

| Switch D Setting | Selected Byte |

|------------------|---------------|

| 8                | 0             |

| 9                | 1             |

| Α                | 2             |

| В                | 3             |

| С                | 4             |

| D                | 5             |

| E                | 6             |

| F                | 7             |

In all floating-point formats, the sign is contained in the high-order bit (bit 0) of byte 0 and the characteristic is contained in bit positions 1 through 7 of byte 0.

In short floating-point formats, the fraction is contained in bytes 1, 2, and 3. In long floating-point formats, the fraction is contained by bytes 1, 2, 3, 4, 5, 6, and 7.

CPU-Registers Stored in Local Storage

During multiplexor-channel operations CPU registers are temporarily stored in local storage. To display or store in this area:

- 1. Set switch C to 5.

- 2. Set switch D to the desired register storage as follows:

|                  | Stored       | Register Selected (General   |

|------------------|--------------|------------------------------|

| Switch D Setting |              | Function)                    |

|                  |              |                              |

| 8                | Il           | (Instruction Address)        |

| 9                | J∮           | (instruction Address)        |

| А                | G            | (Instruction Operation Code) |

| В                | U)           | (Data Address)               |

| С                | v∮           | (Data Mulless)               |

| D                | $\mathbf{L}$ | (Instruction Length)         |

| E                | D            | (General-Purpose Data        |

|                  |              | Register)                    |

| F                | $\mathbf{S}$ | (CPU Status)                 |

Unit Control Word (UCW) Selection

1. Make sure that switch A is set to the proper MPX setting (MPX 0 to MPX 6, depending upon model and features).

| Switch<br>C↓  |       | Control W<br>-A settin |        | ected (depe | ends upon l | JCW capad | city and |

|---------------|-------|------------------------|--------|-------------|-------------|-----------|----------|

| 0             | 0,16  | 32,48                  | 64,80  | 96,112      | 128,144     | 160,176   | 192,208  |

| 1             | 1,17  | 33, 49                 | 65,81  | 97,113      | 129,145     | 161,177   | 193,209  |

| 2             | 2,18  | 34,50                  | 66,82  | 98,114      | 130,146     | 162,178   | 194,210  |

| 3             | 3,19  | 35, 51                 | 67,83  | 99,115      | 131,147     | 163,179   | 195,211  |

| 4             | 4,20  | 36,52                  | 68,84  | 100,116     | 132,148     | 164, 180  | 196,212  |

| 5             | 5,21  | 37, 53                 | 69,85  | 101,117     | 133,149     | 165,181   | 197,213  |

| 6             | 6,22  | 38, 54                 | 70,86  | 102,118     | 134,150     | 166,182   | 198,214  |

| 7             | 7,23  | 39,55                  | 71,87  | 103,119     | 135,151     | 167, 183  | 199,215  |

| 8             | 8,24  | 40,56                  | 72,88  | 104,120     | 136,152     | 168,184   | 200,216  |

| 9             | 9,25  | 41,57                  | 73,89  | 105, 121    | 137,153     | 169,185   | 201,217  |

| A             | 10,26 | 42,58                  | 74, 90 | 106, 122    | 138,154     | 170,186   | 202,218  |

| В             | 11,27 | 43, 59                 | 75, 91 | 107, 123    | 139,155     | 171,187   | 203,219  |

| с             | 12,28 | 44,60                  | 76,92  | 108, 124    | 140,156     | 172,188   | 204, 220 |

| D             | 13,29 | 45,61                  | 77,93  | 109, 125    | 141,157     | 173, 189  | 205, 221 |

| E             | 14,30 | 46,62                  | 78,94  | 110,126     | 142,158     | 174,190   | 206,222  |

| F             | 15,31 | 47,63                  | 79,95  | 111,127     | 143,159     | 175, 191  | 207,223  |

| Switch<br>A → | MPX 0 | MPX 1                  | MPX 2  | MPX 3       | MPX 4       | MPX 5     | MPX 6    |

Figure 6. Selection of Unit Control Words

- 2. Set switch C to select the desired UCW's as shown in Figure 6.

- 3. Set switch D to select the desired byte from the selected UCW as follows:

| Switch D     |               | In UCW (depends upon                |

|--------------|---------------|-------------------------------------|

| Setting      | Byte Selected | setting of switches A and C)        |

|              |               |                                     |

| 0            | 0             | First of two UCW's se-              |

| 1            | 1             | lected by switch C: If,             |

| 2            | 2             | for example, switch A               |

| 3            | 3             | selects MPX 0 and switch            |

| 4            | 4             | C selects UCW's 0 and 16            |

| 5            | 5             | (Figure 6), switch D selects        |

| 6            | 6             | one of bytes 0 through 7            |

| 7            | 7             | in UCW 0. (Thus, if                 |

|              |               | switch D is set to 3, byte          |

|              |               | 3 of UCW 0 is selected.)            |

| 8            | 0             | Second of two UCW's se-             |

| 9            | 1             | lected by switch C: If,             |

| А            | 2             | for example, switch A               |

| В            | 3             | selects MPX 0 and switch            |

| С            | 4             | C selects UCW's 0 and 16            |

| D            | 5             | (Figure 6), switch D se-            |

| E            | 6             | lects <u>one</u> of bytes 0 through |

| $\mathbf{F}$ | 7             | 7 in UCW 16.                        |

|              |               |                                     |

The format of the UCW's is shown in Figure 7. This section presents a description of the contents of UCW bytes.

| Channel | Op and     | Cou  |     |      | Address | Next CCW Address |     |  |  |

|---------|------------|------|-----|------|---------|------------------|-----|--|--|

| Status  | Flags Byte | High | Low | High | Low     | High             | Low |  |  |

| 0       | 1          | 2    | 3   | 4    | 5       | 6                | 7   |  |  |

Figure 7. Unit Control Word Format

Channel Status Byte:

| Bit Function                      |          |

|-----------------------------------|----------|

| 0 Not Used (Channel Data Check) i | in 2030. |

| 1 Channel Control Check           |          |

| 2 Interface Control Check         |          |

| 3 First Status Received*          |          |

| 4 Status Next *                   |          |

| 5 Incorrect Length                |          |

| 6 Program Check                   |          |

| 7 Protection Check                |          |

\*Combinations of Bits 3 and 4 Indicate:

| 3 | 4 |                                    |

|---|---|------------------------------------|

| 0 | 0 | Handling data; expecting data      |

| 0 | 1 | Device instructed to stop;         |

|   |   | expecting status                   |

| 1 | 0 | Status stacked at control unit     |

| 1 | 1 | Status is in Interrupt Buffer (IB) |

|   |   |                                    |

## Op and Flags Byte

| Bit | Function                           |

|-----|------------------------------------|

| 0   | Chain Data Address (CDA)           |

| 1   | Command Chaining (CC)              |

| 2   | Suppress-Length Indication (SLI)   |

| 3   | Skip                               |

| 4   | Program-Controlled Interrupt (PCI) |

| 5   | Active                             |

| 6   | Output (write)                     |

| 7   | Decrement Data Address             |

Current Program-Status-Word (PSW) Selection

The various portions of the current PSW can be displayed at any time that the CPU clock is off and the allow-write indicator is off.

| PSW Field Local Storage Address (Hexadecimal) |                                                                                                                |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| System Mask                                   | B8                                                                                                             |  |  |  |

| Protection Key                                | B9 (high-order four bits). The<br>protection key can also be dis-<br>played from the Q-register.               |  |  |  |

| ASCII Mode                                    | B9 (bit 4)                                                                                                     |  |  |  |

| Machine-Check<br>Mask                         | B9 (bit 5)                                                                                                     |  |  |  |

| PSW Field                                     | Local Storage Address (Hexadecimal)                                                                            |  |  |  |

| Wait State                                    | B9 (bit 6)                                                                                                     |  |  |  |

| Problem State                                 | B9 (bit 7)                                                                                                     |  |  |  |

| Interruption<br>Code                          | (available in old PSW in main<br>storage, bits 16 through 31).                                                 |  |  |  |

| Instruction Length<br>Code                    | 8C (can also be decoded from the two high-order bits of the G register).                                       |  |  |  |

| Condition Code                                | BB (high-order four bits) This<br>is in a four-bit code to corre-<br>spond to the branch-on-condition<br>mask. |  |  |  |

| Program Mask                                  | BB (low-order four bits)                                                                                       |  |  |  |

| Instruction<br>Address                        | (available in LJ register)                                                                                     |  |  |  |

## SINGLE-INSTRUCTION PROCESSING

One method that can be used to debug programs is to process one instruction at a time, service all interruptions, and stop. The next instruction address is then displayed in the B- and A-register display.

To process one instruction at a time:

- 1. Press the Stop key (if necessary to stop proccessing), wait for the Manual light to come on, and then set the Rate switch to the instruction step position (see Figure 2).

- 2. Press the Start key to process each instruction and service all pending interruptions.

When this procedure is used, the program is run basically in the same way as during normal proc-

cessing except that the operation is much slower. Data exchanged between the CPU and I/O devices is not lost when the Rate switch is used as just described. Note, however, that I/O interruptions may occur at different times in the sequence of instructions being processed in single-cycle mode as contrasted with normal instruction processing. That is, an I/O interruption indicating completion of an I/O operation for a relatively slow I/O unit may occur before the start key is pressed for execution of the next instruction. In normal program processing this interruption may occur after several other instructions have been processed. If this difference in time-of-occurrence of an interruption can affect expected program results, a segment of the program should be run (for check-out purposes) rather than only one instruction at a time.

When the CPU stops, the address of the next instruction to be processed is displayed in the B-and A-register indicators.

# SINGLE-CYCLE, DISPLAY, AND STORE OPERATIONS

Although single-cycle operations are intended primarily for Customer Engineering use, you may wish to examine the contents of, or store information into, various registers. An instruction can be processed one <u>machine-cycle</u> at a time and the system stopped after the cycle is completed. To perform this operation: